Siu pins multiplexing control -45, Table 4-24, Table 4-24. siu pins multiplexing control – Motorola MPC8260 User Manual

Page 183

MOTOROLA

Chapter 4. System Interface Unit (SIU)

4-45

Part II. ConÞguration and Reset

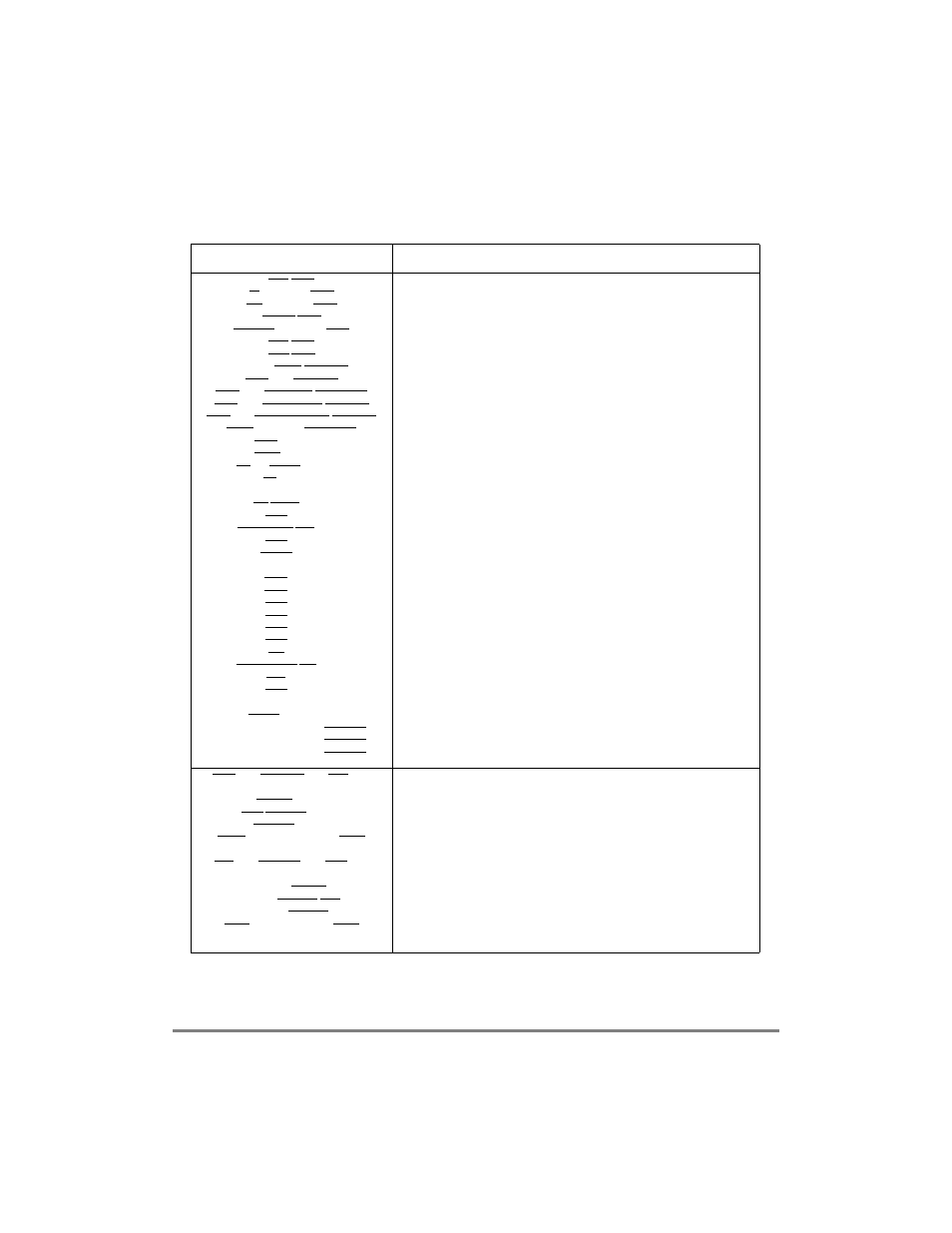

Table 4-24. SIU Pins Multiplexing Control

Pin Name

Pin ConÞguration Control

GBL/IRQ1

CI/BADDR29/IRQ2

WT/BADDR30/IRQ3

L2_HIT/IRQ4

CPU_BG/BADDR31/IRQ5

ABB/IRQ2

DBB/IRQ3

NC/DP0/RSRV/EXT_BR2

IRQ1/DP1/EXT_BG2

IRQ2/DP2/TLBISYNC/EXT_DBG2

IRQ3/DP3/CKSTP_OUT/EXT_BR3

IRQ4/DP4/CORE_SRESET/EXT_BG3

IRQ5/DP5/TBEN/EXT_DBG3

IRQ6/DP6/CSE0

IRQ7/DP7/CSE1

CS[10]/BCTL1/DBG_DIS

CS[11]/AP[0]

PAR/

L_A14

SMI/FRAME/

L_A15

TRDY/

L_A16

CKSTOP_OUT/IRDY/

L_A17

STOP/

L_A18

DEVSEL/

L_A19

IDSEL/

L_A20

PERR/

L_A21

SERR/

L_A22

REQ0/

L_A23

REQ1/

L_A24

GNT0/

L_A25

GNT1/

L_A26

CLK/

L_A27

CORE_SRESET/RST/

L_A28

INTA/

L_A29

LOCK/

L_A30

AD[0–31]/

LCL_D[0Ð31]

C/BE[0–3]/

LCL_DP[0Ð3]

BNKSEL[0]/TC[0]/AP[1]/MODCK1

BNKSEL[1]/TC[1]/AP[2]/MODCK2

BNKSEL[2]/TC[2]/AP[3]/MODCK3

Controlled by SIUMCR programming see Section 4.3.2.6, ÒSIU Module

ConÞguration Register (SIUMCR),Ó for more details.

PWE[0Ð7]/PSDDQM[0Ð7]/PBS[0Ð7]

PSDA10/PGPL0

PSDWE/PGPL1

POE/PSDRAS/PGPL2

PSDCAS/PGPL3

PGTA/PUPMWAIT/PGPL4/PPBS

PSDAMUX/PGPL5

LBS[0Ð3]/LSDDQM[0Ð3]/LWE[0Ð3]

LGPL0/LSDA10

LGPL1/LSDWE

LGPL2/LSDRAS/LOE

LGPL3/LSDCAS

LPBS/LGPL4/LUPWAIT/LGTA

LGPL5/LSDAMUX

Controlled dynamically according to the speciÞc memory controller

machine that handles the current bus transaction.