Motorola MPC8260 User Manual

Page 127

MOTOROLA

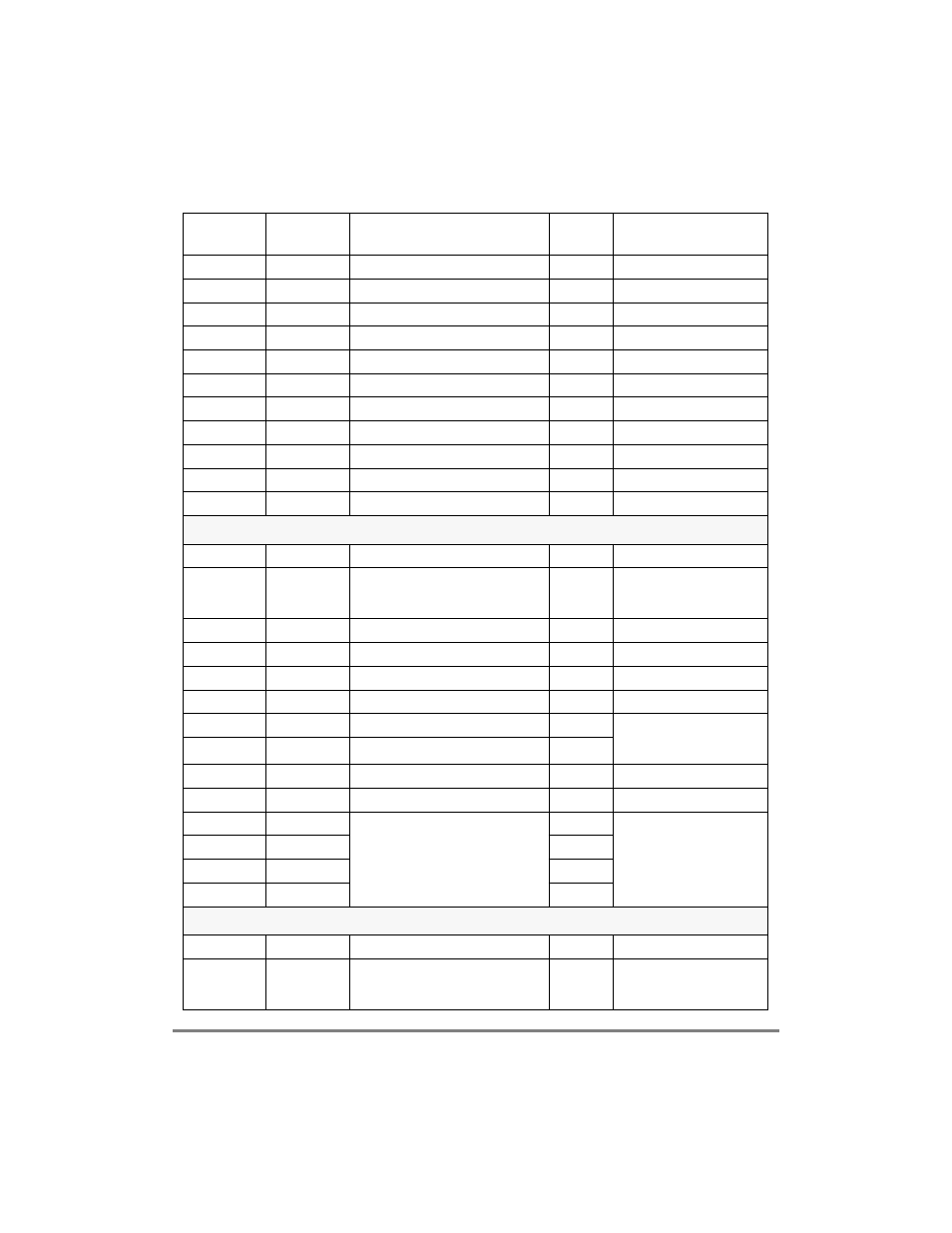

Chapter 3. Memory Map

3-7

Part I. Overview

11029

Reserved

Ñ

24 bits

Ñ

1102C

IDMR2

IDMA 2 mask register

8 bits

1102D

Reserved

Ñ

24 bits

Ñ

11030

IDSR3

IDMA 3 event register

8 bits

11031

Reserved

Ñ

24 bits

Ñ

11034

IDMR3

IDMA 3 mask register

8 bits

11035

Reserved

Ñ

24 bits

Ñ

11038

IDSR4

IDMA 4 event register

8 bits

11039

Reserved

Ñ

24 bits

Ñ

1103C

IDMR4

IDMA 4 mask register

8 bits

1103DÐ112FF

Reserved

Ñ

707 bytes

Ñ

FCC1

11300

GFMR1

FCC1 general mode register

32 bits

11304

FPSMR1

FCC1 protocol-speciÞc mode register

32 bits

29.13.2/29-85 (ATM)

30.18.1/30-20 (Ethernet)

31.6/31-7 (HDLC)

11308

FTODR1

FCC1 transmit on demand register

16 bits

1130A

Reserved

Ñ

2 bytes

Ñ

1130C

FDSR1

FCC1 data synchronization register

16 bits

1130E

Reserved

Ñ

2 bytes

Ñ

11310

FCCE1

FCC1 event register

32 bits

29.13.3/29-87 (ATM)

30.18.2/30-21 (Ethernet)

31.9/31-14 (HDLC)

11314

FCCM1

FCC1 mask register

32 bits

11318

FCCS1

FCC1 status register

8 bits

11319

Reserved

Ñ

3 bytes

Ñ

1131C

FTIRR1_PHY0 FCC1 transmit internal rate registers

for PHY0Ð3

8 bits

1131D FTIRR1_PHY1

8

bits

1131E FTIRR1_PHY2

8

bits

1131F FTIRR1_PHY3

8

bits

FCC2

11320

GFMR2

FCC2 general mode register

32 bits

11324

FPSMR2

FCC2 protocol-speciÞc mode register

32 bits

29.13.2/29-85 (ATM)

30.18.1/30-20 (Ethernet)

31.6/31-7 (HDLC)

Table 3-1. Internal Memory Map (Continued)

Internal

Address

Abbreviation

Name

Size

Section/Page Number