6 effect of port size on data transfers, Effect of port size on data transfers -16 – Motorola MPC8260 User Manual

Page 248

8-16

MPC8260 PowerQUICC II UserÕs Manual

MOTOROLA

Part III. The Hardware Interface

software attempt to align code and data where possible.

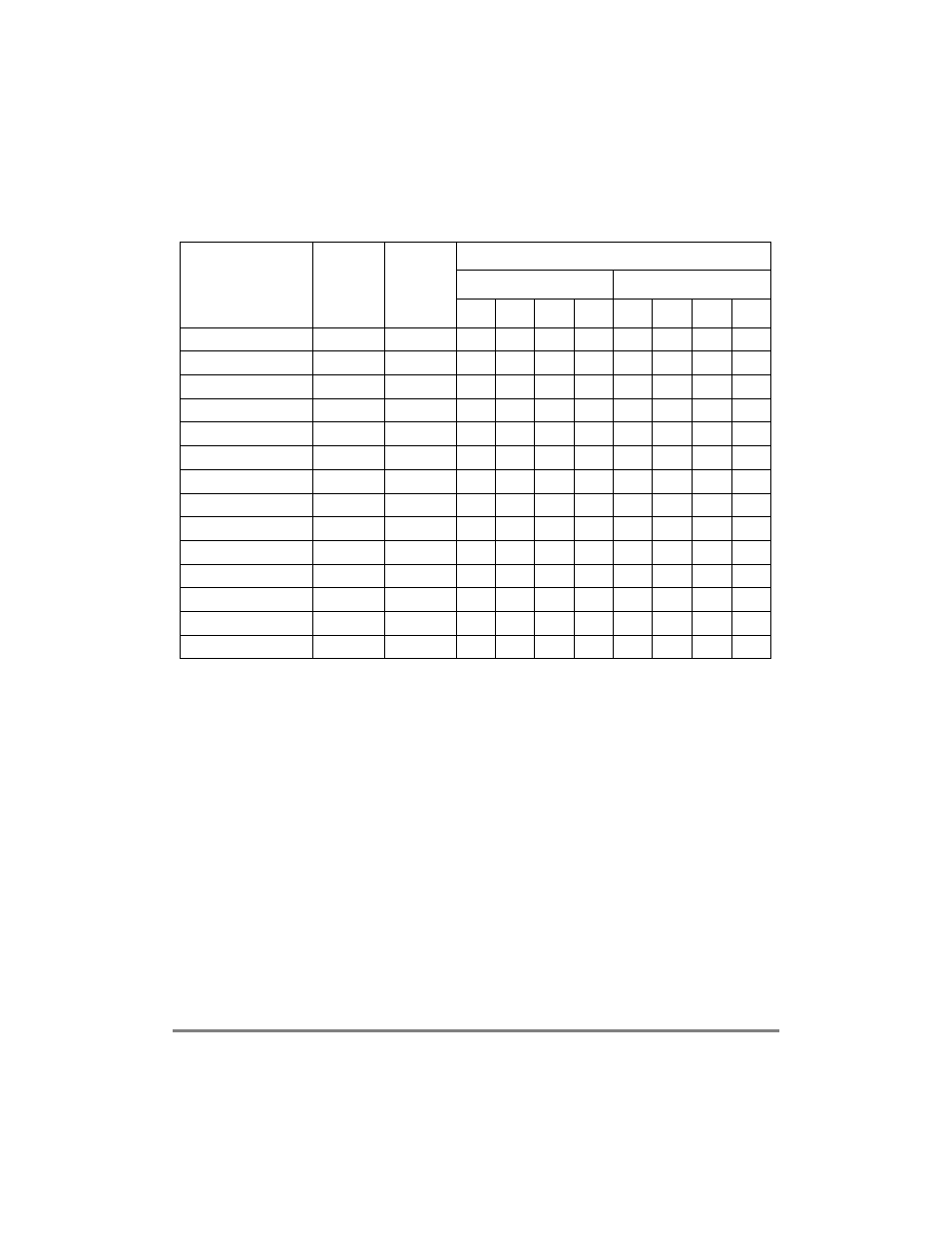

8.4.3.6 Effect of Port Size on Data Transfers

The MPC8260 can transfer operands through its 64-bit data port. If the transfer is controlled

by the internal memory controller, the MPC8260 can support 8-, 16-, 32-, and 64-bit data

port sizes. The bus requires that the portion of the data bus used for a transfer to or from a

particular port size be Þxed. A 64-bit port must reside on data bus bits D[0Ð63], a 32-bit

port must reside on bits D[0Ð31], a 16-bit port must reside on bits D[0Ð15], and an 8-bit

port must reside on bits D[0Ð7]. The MPC8260 always tries to transfer the maximum

amount of data on all bus cycles: for a word operation, it always assumes the port is 64 bits

wide when beginning the bus cycle; for burst and extended byte cycles, a 64-bit bus is

assumed.

Figure 8-6 shows the device connections on the data bus. Table 8-8 lists the bytes required

on the data bus for read cycles.

Table 8-7. Unaligned Data Transfer Example (4-Byte Example)

Program Size of

Word (4 bytes)

TSIZ[1Ð3]

A[29Ð31]

Data Bus Byte Lanes

D0... ...D31

D32... ...D63

B0

B1

B2

B3

B4

B5

B6

B7

Aligned

1 0 0

0 0 0

A

1

1

A: Byte lane used

A

A

A

С

2

2

С: Byte lane not used

С

С

С

MisalignedÑ1st access

0 1 1

0 0 1

Ñ

A

A

A

С

С

С

С

2nd access

0 0 1

1 0 0

С

С

С

С

A

С

С

С

MisalignedÑ1st access

0 1 0

0 1 0

С

С

A

A

С

С

С

С

2nd access

0 1 0

1 0 0

С

С

С

С

A

A

С

С

MisalignedÑ1st access

0 0 1

0 1 1

С

С

С

A

С

С

С

С

2nd access

0 1 1

1 0 0

С

С

С

С

A

A

A

Ñ

Aligned

1 0 0

1 0 0

С

С

С

С

A

A

A

A

MisalignedÑ1st access

0 1 1

1 0 1

С

С

С

С

С

A

A

A

2nd access

0 0 1

0 0 0

A

С

С

С

С

С

С

С

MisalignedÑ1st access

0 1 0

1 1 0

С

С

С

С

С

С

A

A

2nd access

0 1 0

0 0 0

A

A

С

С

С

С

С

С

MisalignedÑ1st access

0 0 1

1 1 1

С

С

С

С

С

С

С

A

2nd access

0 1 1

0 0 0

A

A

A

С

С

С

С

С