Motorola MPC8260 User Manual

Page 833

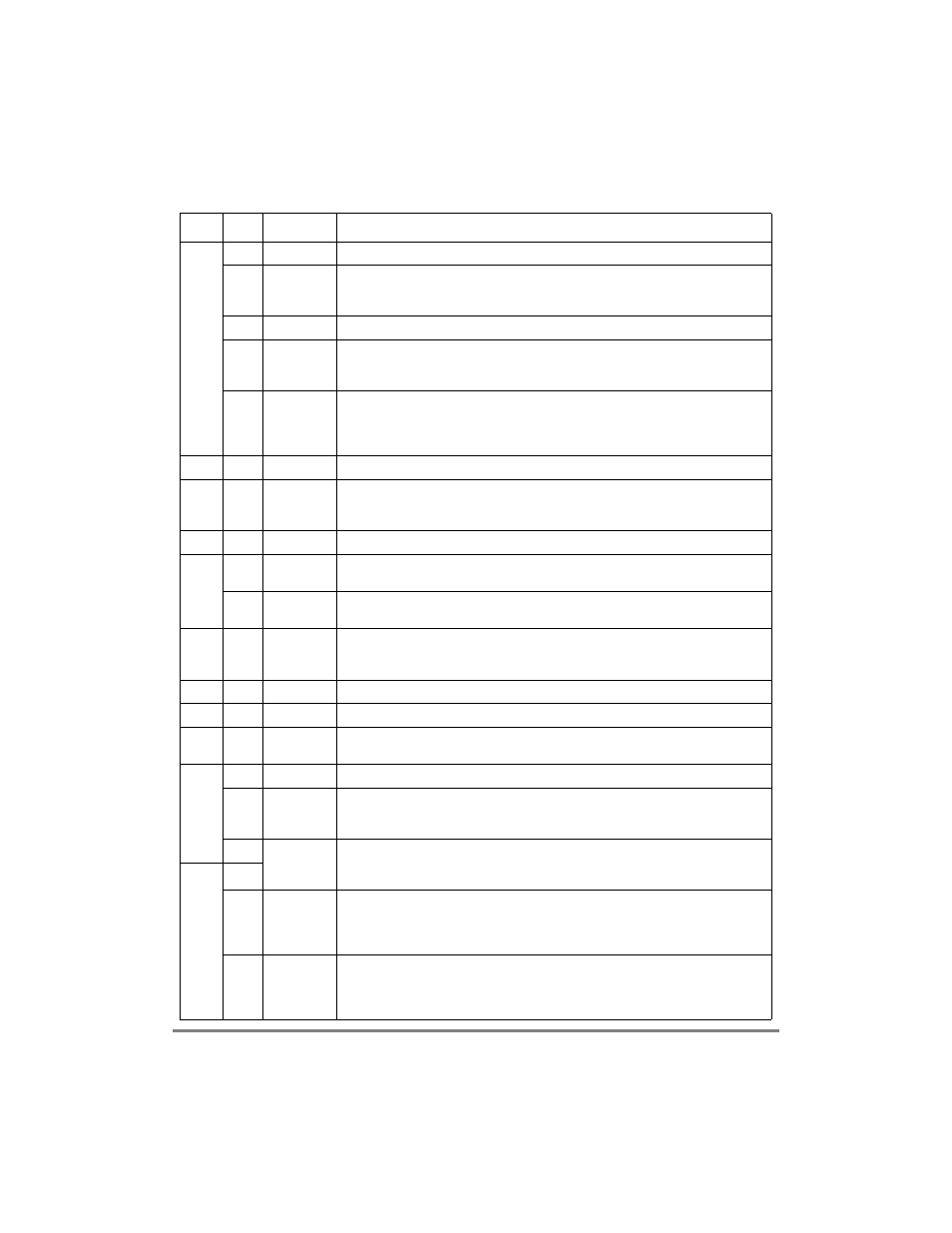

29-53

MPC8260 PowerQUICC II UserÕs Manual

MOTOROLA

Part IV. Communications Processor Module

0x02

0

Ñ

Internal use only. Initialize to 0.

1

INF

Used for AAL5 Only. Indicates the transmitter state. Initialize to 0

0 In idle state.

1 In AAL5 frame transmission state.

2Р11

С

Internal use only. Initialize to 0.

12

ABRF

Used for AAL5 Only.

0 ABR Flow control is disabled.

1 ABR Flow control is enabled.

13Ð15

AAL

AAL type

000 AAL0ÑSegmentation without any adaptation layer.

001 AAL1ÑATM adaptation layer 1 protocol.

010 AAL5ÑATM adaptation layer 5 protocol.

0x04

Ñ

TxDBPTR

Tx data buffer pointer. Holds the real address of the current position in the Tx buffer.

0x08

Ñ

TBDCNT

Transmit BD count. Counts the remaining data to transmit in the current transmit buffer.

Its initial value is loaded from the data length Þeld of the TxBD when a new buffer is

open; its value is subtracted for any transmitted cell associated with this channel.

0x0A

Ñ

TBD_OffSet

Transmit BD offset. Holds offset from TBD_BASE of the current BD. Initialize to 0.

0x0C

0Ð7

Rate

Reminder

Rate remainder. Used by the APC to hold the rate remainder after adding the pace

fraction to the additive channel rate. Initialize to 0.

8Ð15

PCR Fraction Peak cell rate fraction. Holds the peak cell rate fraction of this channel in units of 1/256

slot. If this is an ABR channel, this Þeld is automatically updated by the CP.

0x0E

Ñ

PCR

Peak cell rate. Holds the peak cell rate (in units of APC slots) permitted for this channel

according to the trafÞc contract. Note that for an ABR channel, the CP automatically

updates PCR to the ACR value.

0x10

С

С

Protocol-speciÞc

0x16

Ñ

APCLC

APC linked channel. Used by the CP. Initialize to 0 (null pointer).

0x18

Ñ

ATMCH

ATM cell header. Holds the full (4-byte) ATM cell header of the current channel. The

transmitter appends ATMCH to the cell payload during transmission.

0x1C

0Р1

С

Reserved, should be cleared.

2Ð7

PMT

Performance monitoring table. Points to one of the available 64 performance

monitoring tables. The starting address of the table is PMT_BASE+PMT

´ 32. Can be

changed on-the-Яy.

8Р15

TBD_BASE

TxBD base. Points to the Þrst BD in the channelÕs TxBD table. The 8 most-signiÞcant

bits of the address are taken from BD_BASE_EXT in the parameter RAM. The four

least-signiÞcant bits of the address are taken as zero.

0x1E

0Ð11

12

BNM

Buffer-not-ready interrupt mask. Can be changed on-the-ßy.

0 The transmit buffer-not-ready event of this channel is masked. (TBNR event is not

sent to the interrupt queue.)

1 The buffer-not-ready event of this channel is enabled.

13

STPT

Stop transmit. Initialize to 0. When the host sets this bit, the CP deactivates this

channel and clears TCT[VCON] when the channel is next encountered in the APC

scheduling table. Note that for AAL5 if STPT is set and frame transmission is already

started (TCT[INF]=1), an abort indication will be sent (last cell with zero length Þeld).

Table 29-21. TCT Field Descriptions (Continued)

Offset

Bits

Name Description