Microprocessor -30, Integer divide latency -30, The new latenc y is reßected in table 2-6 – Motorola MPC8260 User Manual

Page 118

2-30

MPC8260 PowerQUICC II UserÕs Manual

MOTOROLA

Part I. Overview

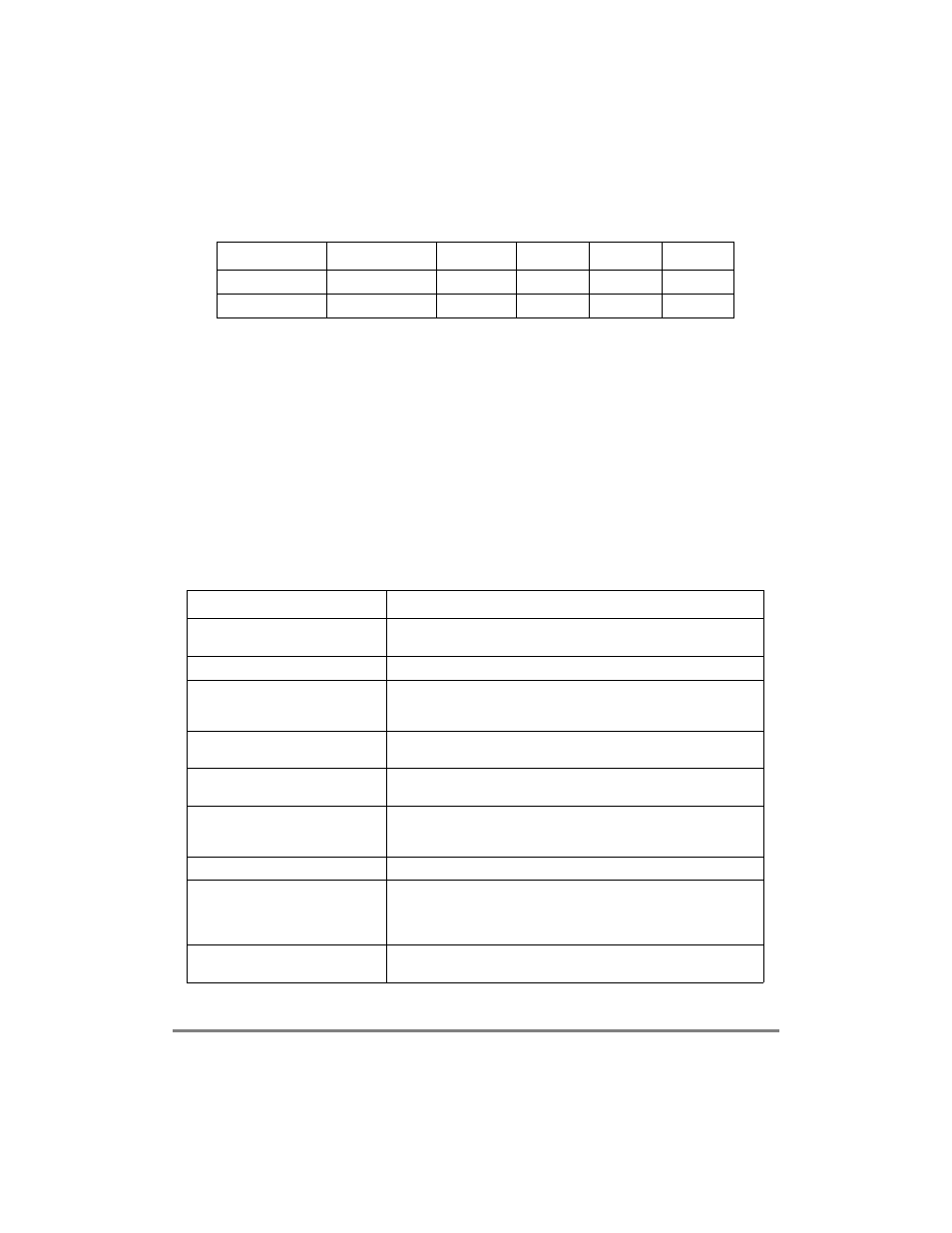

The new latency is reßected in Table 2-6.

2.8 Differences between the MPC8260Õs Core and the

PowerPC 603e Microprocessor

The MPC8260Õs processor core is a derivative of the MPC603e microprocessor design.

Some changes have been made and are visible either to a programmer or a system designer.

Any software designed around an MPC603e is functional when replaced with the

MPC8260 except for the speciÞc customer-visible changes listed in Table 2-7.

Software can distinguish between the MPC603e and the MPC8260 by reading the

processor version register (PVR). The MPC8260Õs processor version number is 0x0081; the

processor revision level starts at 0x0100 and is incremented for each revision of the chip.

Table 2-6. Integer Divide Latency

Primary Opcode

Extended Opcode

Mnemonic

Form

Unit

Cycles

31

459

divwu[o][.]

xo

IU

20

31

491

divw[o][.]

xo

IU

20

Table 2-7. Major Differences between MPC8260Õs Core and the MPC603e UserÕs

Manual

Description

Impact

Added bus multipliers of 4.5x, 5x, 5.5x,

6x, 6.5x 7x, 7.5x, 8x

Occupies unused encodings of the PLL_CFG[0Ð4]

No FPU

Floating-point arithmetic instructions are not supported in hardware.

Added hardware support for

misaligned little endian accesses

Except for strings/multiples, little-endian load/store accesses not on a word

boundary generate exceptions under the same circumstances as big-

endian accesses.

Removed misalignment support for

eciwx and ecowx instructions.

These instructions take an alignment exception if not on a word boundary.

Added ability to broadcast dcbf, dcbi,

and dcbst onto the 60x bus

Setting HID0[ABE] enables the new broadcast feature (new in the PID7v-

603e). The default is to not broadcast these operations.

Added ability to reßect the value of the

M bit onto the 60x bus during

instruction translations

Setting HID0[IFEM] enables this feature. The default is to not present the M

bit on the bus.

Removed HID0[EICE]

There is no support for ICE pipeline tracking.

Added instruction and data cache

locking mechanism

Implements a cache way locking mechanism for both the instruction and

data caches. One to three of the four ways in the cache can be locked with

control bits in the HID2 register. See Section 2.3.1.2.3, ÒHardware

Implementation-Dependent Register 2 (HID2).Ó

Added pin-conÞgurable reset vector

The value of MSR[IP], interrupt preÞx, is determined at hard reset by the

hardware conÞguration word.