7 serial interface gci support, Serial interface gci support -31, Gci signals -31 – Motorola MPC8260 User Manual

Page 485

MOTOROLA

Chapter 14. Serial Interface with Time-Slot Assigner

14-31

Part IV. Communications Processor Module

19. SI1CMDR is not used.

20. SI1STR does not need to be read.

21. ConÞgure the SCC1 for HDLC operation (to handle the LAPD protocol of the D

channel), and conÞgure SCC2 and SMC1 as preferred.

22. SI1GMR = 0x01. Enable TDM A (one static TDM).

23. Enable SCC1, SCC2 and SMC1.

14.7 Serial Interface GCI Support

The MPC8260 fully supports the normal mode of the GCI, also known as the ISDN-

oriented modular revision 2.2 (IOM-2), and the SCIT. The MPC8260 also supports the D-

channel access control in S/T interface terminals using the command/indication (C/I)

channel.

The GCI bus consists of four linesÑtwo data lines, a clock, and a frame synchronization

line. Usually, an 8-kHz frame structure deÞnes the various channels within the 256-kbps

data rate. The MPC8260 supports two (limited by the number of SMCs) independent GCI

buses, each with independent receive and transmit sections. The interface can also be used

in a multiplexed frame structure on which up to eight physical layer devices multiplex their

GCI channels. In this mode, the data rate would be 2,048 kbps.

In the GCI bus, the clock rate is twice the data rate. The SI divides the input clock by two

to produce the data clock. The MPC8260 also has data strobe lines and the 1

´ data rate

clock L1CLKOx output pins. These signals are used for interfacing devices to GCI that do

not support the GCI bus. Table 14-11 describes GCI signals for each transmit and receive

channel.

The GCI bus signals are shown in Figure 14-24.

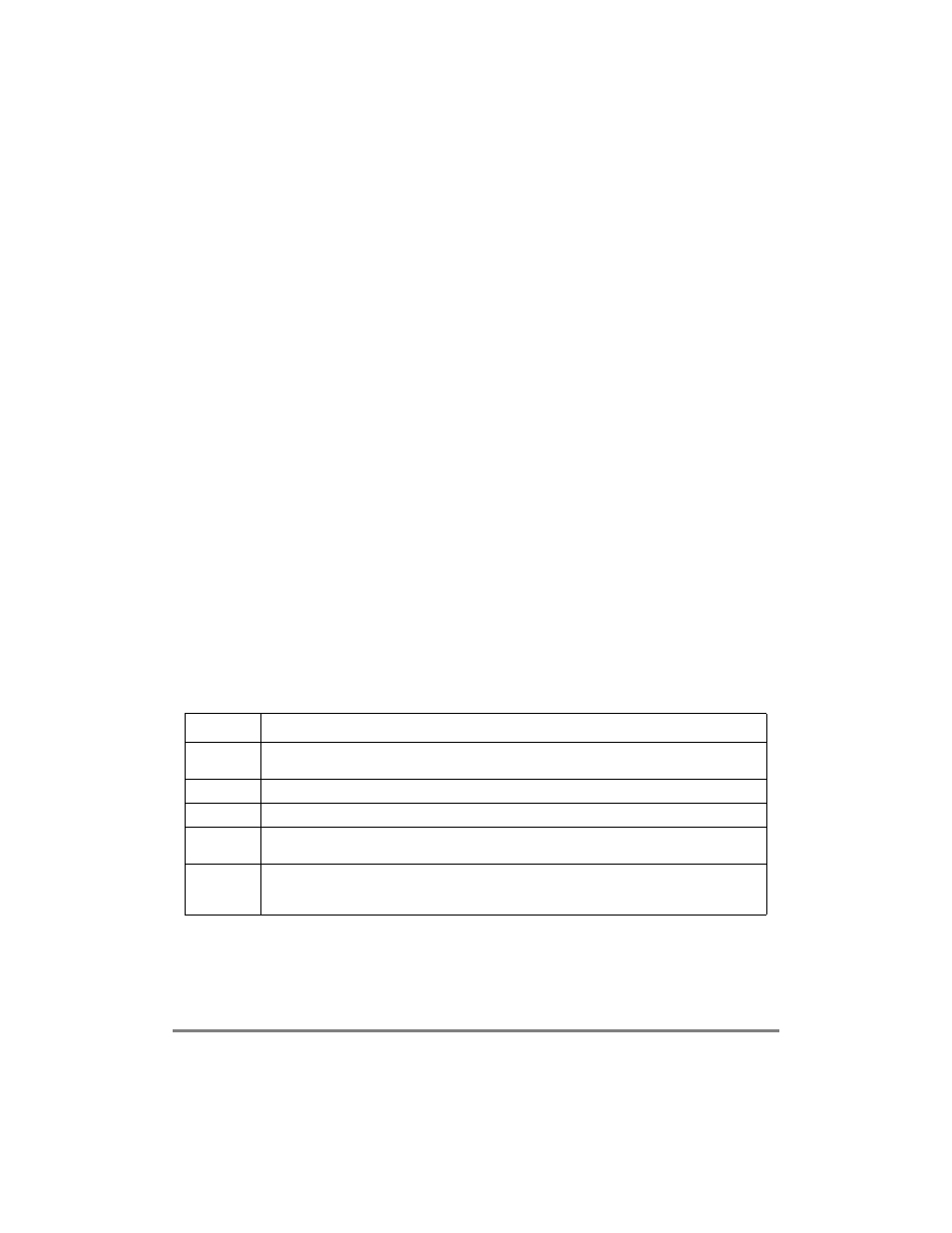

Table 14-11. GCI Signals

Signal

Description

L1RSYNCx

Used as a GCI sync signal; input to the MPC8260. This signal indicates that the clock periods

following the pulse designate the GCI frame.

L1RCLKx

Used as a GCI clock; input to the MPC8260. The L1RCLKx signal frequency is twice the data clock.

L1RXDx

Used as a GCI receive data; input to the MPC8260.

L1TXDx

Used as a GCI transmit data; open-drain output. Valid only for the bits that are supported by the IDL;

otherwise, three-stated.

L1CLKOx

Optional signal; output from the MPC8260. This 1

´ clock output is used to clock devices that do not

interface directly to the GCI. If the double-speed clock is used, (DSCx bit is set in the SIxMR), this

output is the L1RCLKx divided by 2; otherwise, it is simply a 1

´ output of the L1RCLKx signal.

Note: x = a, b, c, and d for TDMa, TDMb, TDMc, and TDMd (for SI1 and SI2).