12 sdram configuration examples, Sdram configuration examples -48, Sdram bank-staggered cbr refresh timing -48 – Motorola MPC8260 User Manual

Page 324: 60x address bus partition -48, 12 sdram conþguration examples

10-48

MPC8260 PowerQUICC II UserÕs Manual

MOTOROLA

Part III. The Hardware Interface

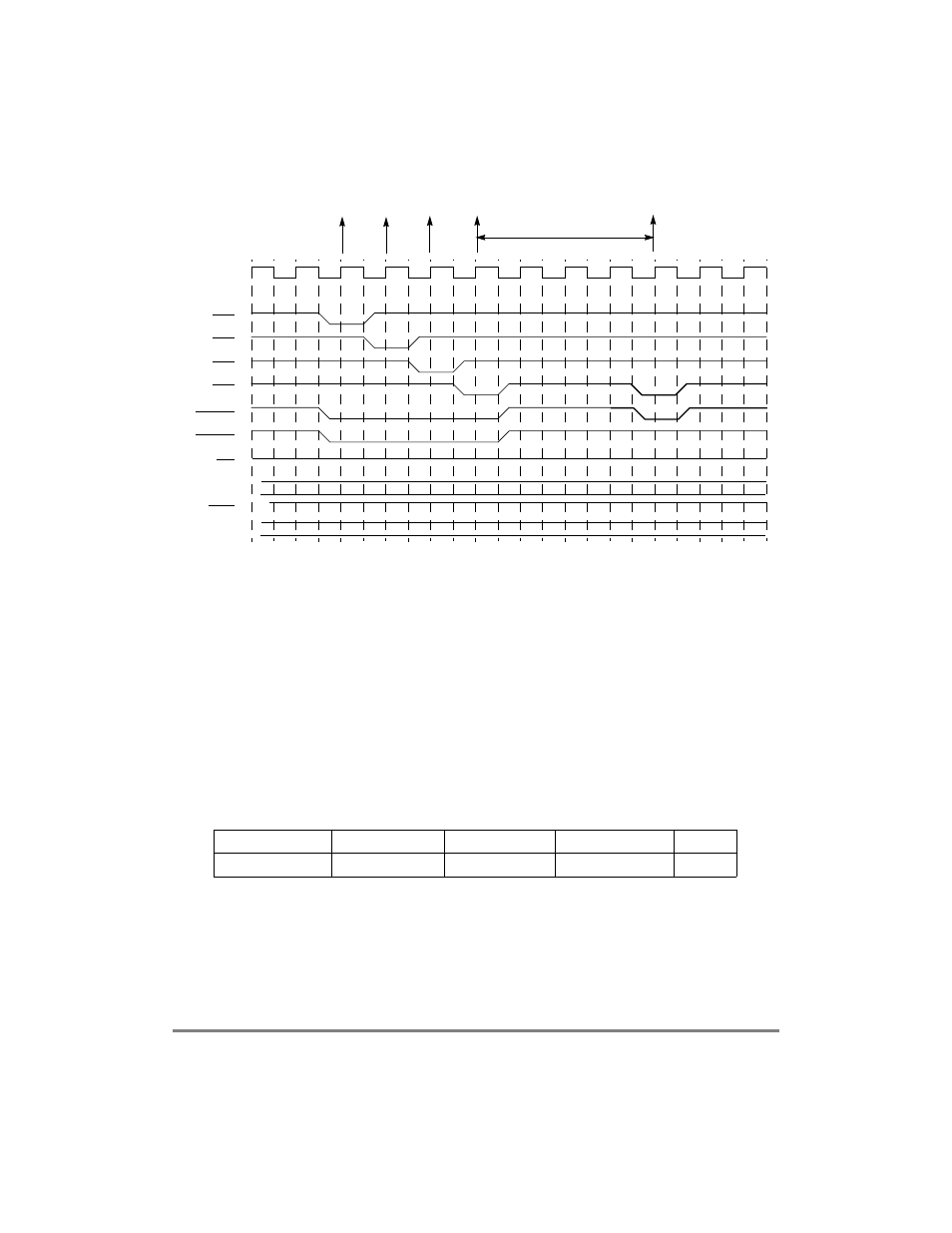

Figure 10-39. SDRAM Bank-Staggered CBR Refresh Timing

10.4.12 SDRAM ConÞguration Examples

The following sections provide SDRAM conÞguration examples for page- and bank-based

interleaving.

10.4.12.1 SDRAM ConÞguration Example (Page-Based Interleaving)

Consider the following SDRAM organization:

¥

64-bit port size organized as 8 x 8 x 64 Mbit.

¥

Each device has 4 internal banks, 12 rows, and 9 columns

For page-based interleaving, the address bus should be partitioned as shown in Table 10-21.

The following parameters can be extracted:

¥

PSDMR[PBI] = 1ÑPage-based interleaving

¥

ORx[BPD] = 01ÑFour internal banks

¥

ORx[ROWST] = 0110ÑRow starts at A[6]

¥

ORx[NUMR] = 011ÑTwelve row lines

Table 10-21. 60x Address Bus Partition

A[0Ð5]

A[6Ð17]

A[18Ð19]

A[20Ð28]

A[29Ð31]

msb of start address

Row

Bank select

Column

lsb

CLK

ALE

CS0

SDRAS

SDCAS

MA[0Ð11]

WE

DQM

Data

CS1

CS2

CS3

RFRC

CBR

CBR

CBR

CBR

Activate

Z