Fcc transmit internal rate clocking -89, Fcc transmit internal rate registers (ftirrx) -89, Ftirrx field descriptions -89 – Motorola MPC8260 User Manual

Page 869: In figure 29-61, includes the initial v

MOTOROLA

Chapter 29. ATM Controller

29-89

Part IV. Communications Processor Module

Table 29-49 describes FTIRRx Þelds.

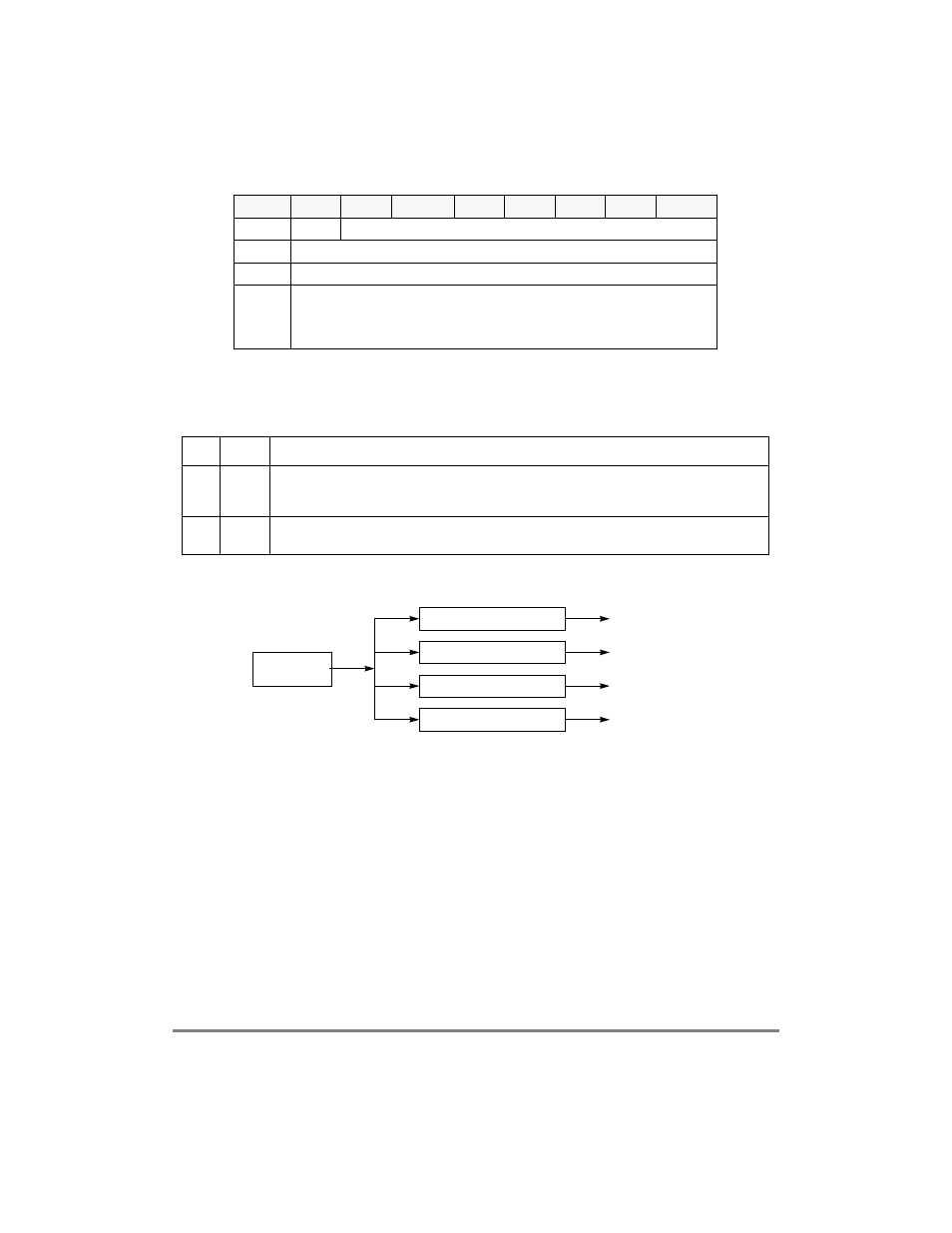

Figure 29-62 shows how transmit clocks are determined.

.

Figure 29-62. FCC Transmit Internal Rate Clocking

Example:

Suppose the MPC8260 is connected to four 155 Mbps PHY devices and the maximum

transmission rate is 155 Mbps for the Þrst PHY and 10 Mbps for the rest of the PHYs. The

BRG CLK should be set according to the highest rate. If the system clock is 133 MHz, the

BRG should be programmed to divide the system clock by 362 to generate cell transmit

requests every 362 system clocks:

For the 155 Mbps PHY, the FTIRR divider should be programmed to zero (the BRG CLK

is divided by one); for the rest of the 10 Mbps PHYs, the FTIRR divider should be

programmed to 14 (the BRG CLK is divided by 15).

Bits

0

1

2

3

4

5

6

7

Field

TRM

Initial Value

Reset

0000_0000

R/W

R/W

Address

FCC1: 0x1131F (FTIRR1_PHY0), 0x1131D (FTIRR1_PHY1),

0x1131E (FTIRR1_PHY2), 0x1131F (FTIRR1_PHY3)

FCC2: 0x1133F (FTIRR2_PHY0), 0x1133D (FTIRR2_PHY1),

0x1133E (FTIRR2_PHY2), 0x1133F (FTIRR2_PHY3)

Figure 29-61. FCC Transmit Internal Rate Registers (FTIRRx)

Table 29-49. FTIRRx Field Descriptions

Bits

Name

Description

0

TRM

Transmit mode.

0 External rate mode.

1 Internal rate mode.

1Ð7

Initial

Value

The initial value of the internal rate timer. A value of 0x7F produces the minimum clock rate (BRG

CLK divided by 128); 0x00 produces the maximum clock rate (BRG CLK divided by 1).

BRG CLK

PHY#0 Internal Rate Timer

PHY# 0 Tx Rate

PHY# 1 Tx Rate

PHY# 2 Tx Rate

PHY# 3 Tx Rate

PHY#3 Internal Rate Timer

PHY#2 Internal Rate Timer

PHY#1 Internal Rate Timer

133MHz

53

8

´

(

)

´

(

)

155.52Mbps

-----------------------------------------------------

362

=