2 vc-level address compression tables (vclts), 3 misinserted cells, Vc-level address compression tables (vclts) -18 – Motorola MPC8260 User Manual

Page 798: Misinserted cells -18, Vp pointer address compression -18, Vc pointer address compression -18

29-18

MPC8260 PowerQUICC II UserÕs Manual

MOTOROLA

Part IV. Communications Processor Module

Figure 29-7 shows the VP pointer address compression from Table 29-5.

Figure 29-7. VP Pointer Address Compression

29.4.2.2 VC-Level Address Compression Tables (VCLTs)

Each VPLT entry points to a single VCLT. Like the VPLT, the size of each VCLT depends

on VC_MASK. Because the VCLT contains word entries, if VC_MASK =

0b11_1111_1111, the table is 4 Kbytes. The address of an entry in this table is VCT_BASE

+ VCOFFSET

´ 4 + VCpointer ´ 4.

The MPC8260 can check that all unallocated VCI bits are 0 by setting GMODE[CUAB]

(check unallocated bits). If they are not, the cell is considered a misinserted cell.

An example of VC-level table entry address calculation is shown in Table 29-6. Note that

VCOFFSET is assumed to be 0x100 for this example.

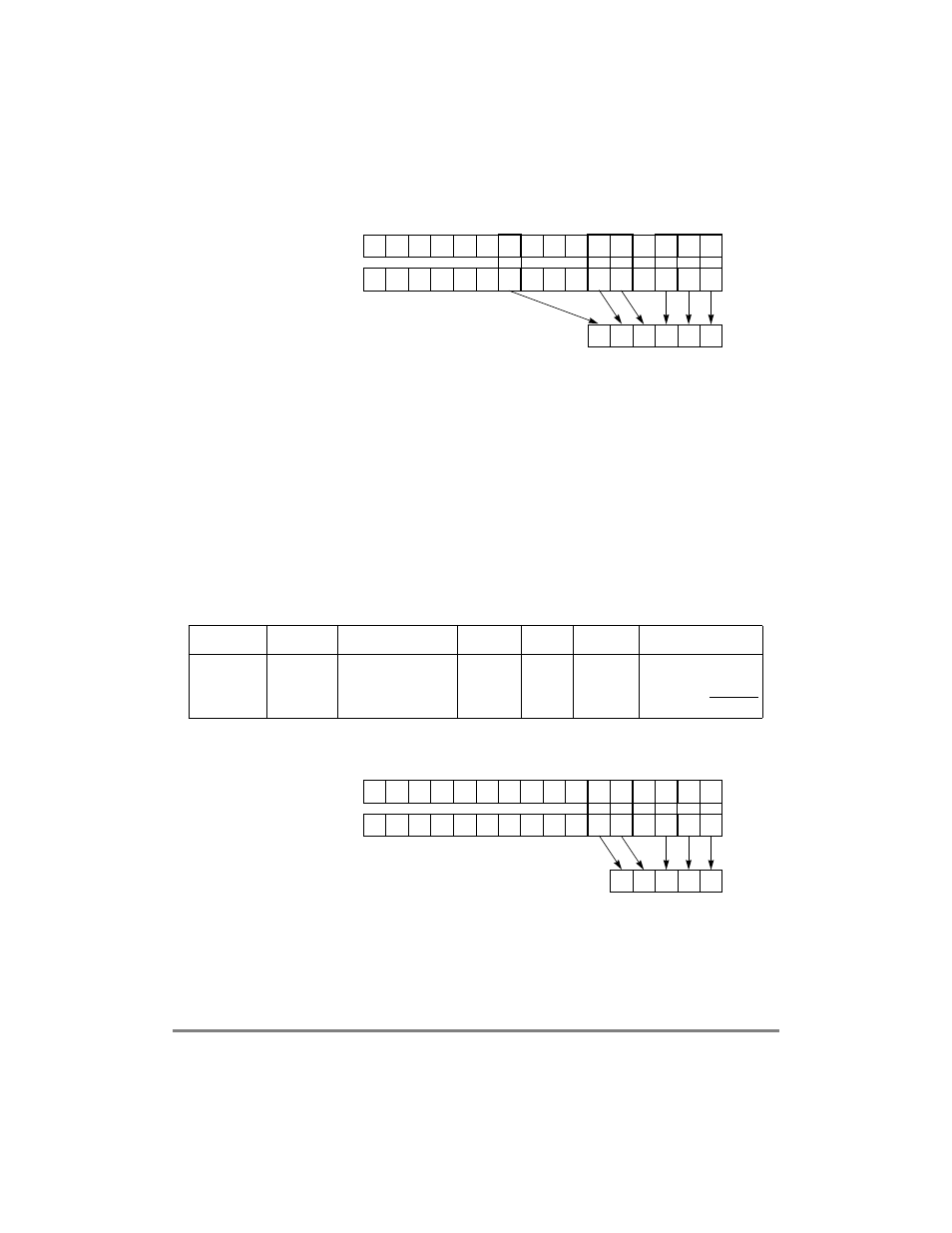

Figure 29-8 shows the VC pointer address compression from Table 29-6.

Figure 29-8. VC Pointer Address Compression

29.4.3 Misinserted Cells

If the address lookup mechanism cannot find a match (MS=1), the cell is discarded and

ATM layer statistics are updated, as described in Section 29.8, ÒATM Layer Statistics.Ó

Table 29-6. VC-Level Table Entry Address Calculation Example

VCT_BASE

VCOffset

VC-Level Table Size

VC_MASK

VCI

VC Pointer

VC Entry Address

0x0084_0000

0x0100

32 entries

0x0037

0x0031

0x19

VC Base = 0x840000

0x100 x 4 = 0x000400

0x19 x 4 = 0x000064

0x840464

0

0

0

0

0

0

0

1

0

0

0

1

0

0

1

0

0

0

1

1

0

1

1

1

0

0

1

PHY+VPI

VP_MASK

VP Pointer

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

0

0

0

1

0

0

0

0

0

0

1

1

0

1

1

1

0

0

1

VCI

VC_MASK

VC Pointer

1

1

0

0

0

0

0

0

0

0