4 i2c multi-master considerations, C multi-master considerations – Motorola MPC8260 User Manual

Page 947

MOTOROLA

Chapter 34. I2C Controller

34-5

Part IV. Communications Processor Module

If the MPC8260 is the slave target of the read, prepare the I

2

C transmit buffers and BDs and

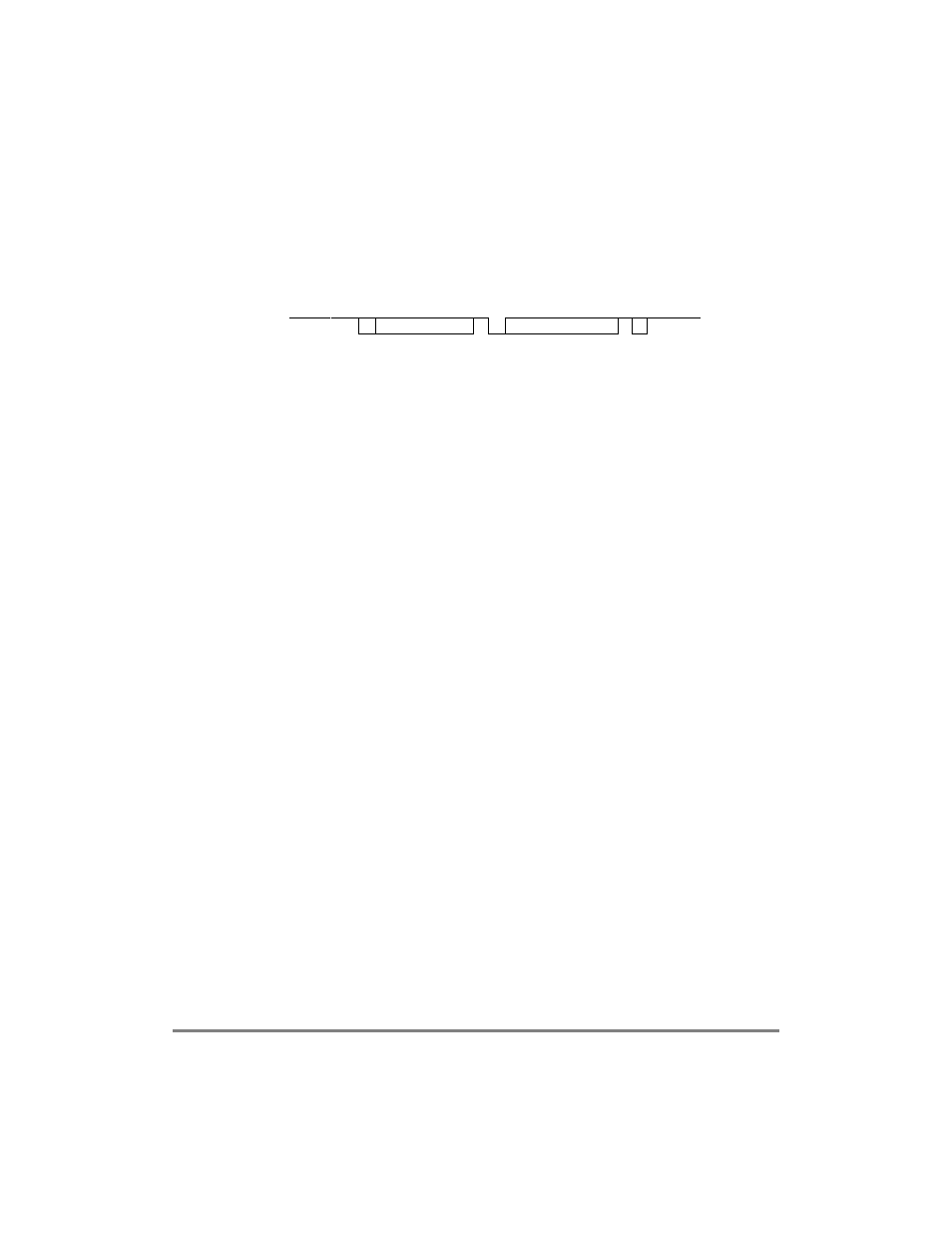

activate it by setting I2COM[STR]. Figure 34-5 shows the timing for a master read.

Figure 34-5. I

2

C Master Read Timing

A master read occurs as follows:

1. Set the masterÕs I2COM[STR] to initiate the read. The transfer starts when the

SDMA channel loads the transmit FIFO with data and the I

2

C bus is not busy.

2. The slave detects a start condition on SDA and SCL.

3. After the Þrst byte is shifted in, the slave compares the received data to its slave

address. If the slave is an MPC8260, the address is programmed in its I

2

C address

register (I2ADD).

Ñ If a match is found, the slave acknowledges the received byte and begins

transmitting on the clock pulse immediately following the acknowledge.

Ñ If a match is found but the slave is not ready, the read request is not

acknowledged and the transaction is aborted. If the slave is an MPC8260, a

maskable transmission error interrupt is triggered to allow software to prepare

data for transmission on the next try.

Ñ If a mismatch occurs, the slave ignores the message and searches for a new start

condition.

4. The master acknowledges each byte sent as long as an overrun does not occur. If the

master receiver fails to acknowledge a byte, the slave aborts transmission. For a

slave MPC8260, the abort generates a maskable interrupt. A maskable interrupt is

also issued after a complete buffer is sent or after an error. If an underrun occurs, the

MPC8260 slave sends ones until a stop condition is detected.

34.3.4 I

2

C Multi-Master Considerations

The I

2

C controller supports a multi-master conÞguration, in which the I

2

C controller must

alternate between master and slave modes. The I

2

C controller supports this by

implementing I

2

C master arbitration in hardware. However, due to the nature of the I

2

C bus

and the implementation of the I

2

C controller, certain software considerations must be made.

SDA

Data Byte

Device Address

R

S

T

O

P

S

T

A

R

T

N

O

A

C

K

A

C

K

Note: After the nth data byte, the master does not acknowledge the slave.