2 cmx si1 clock route register (cmxsi1cr), Cmx si1 clock route register (cmxsi1cr) -10, Multi-phy receive address multiplexing -10 – Motorola MPC8260 User Manual

Page 500: Figure 15-7

15-10

MPC8260 PowerQUICC II UserÕs Manual

MOTOROLA

Part IV. Communications Processor Module

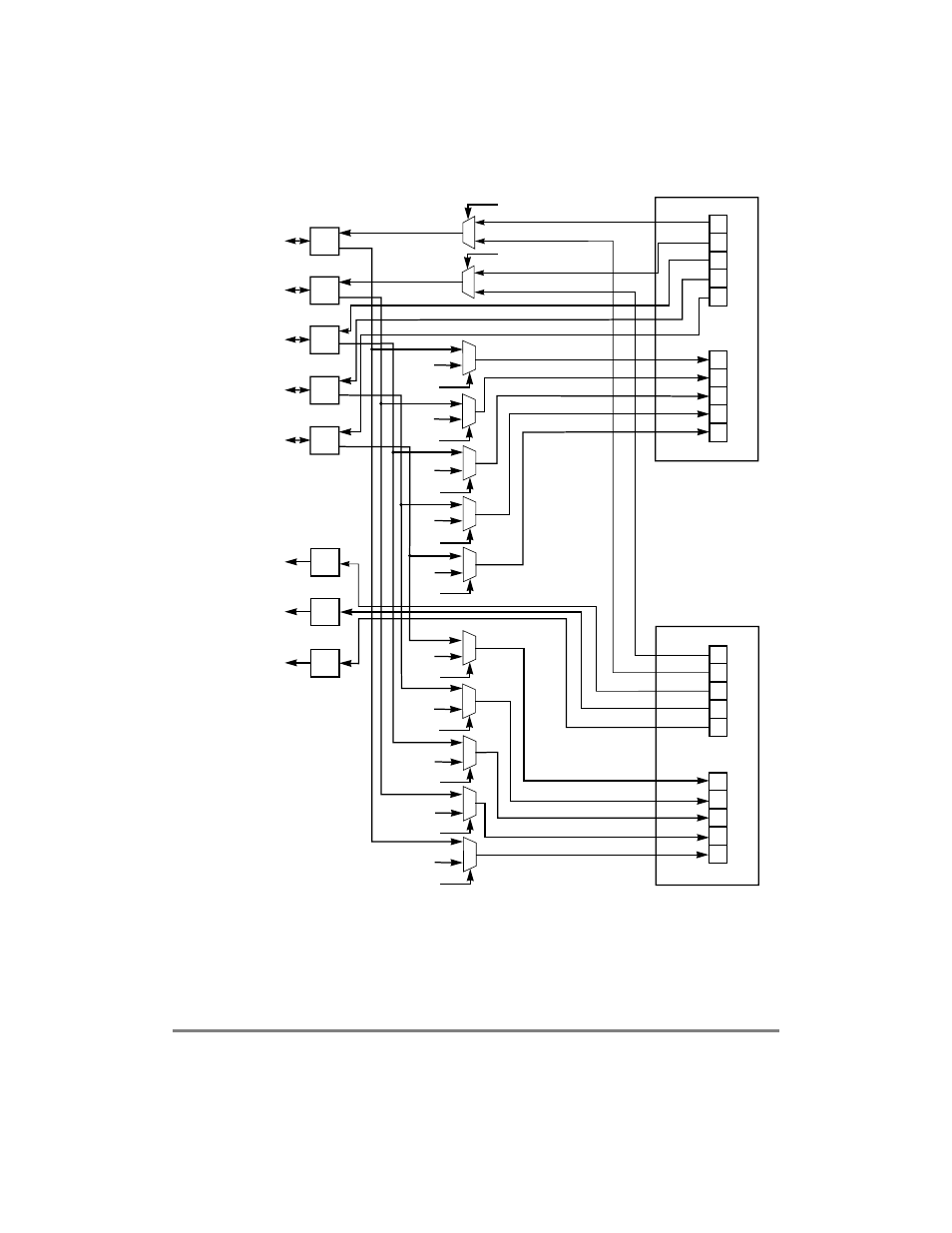

Figure 15-7. Multi-PHY Receive Address Multiplexing

15.4.2 CMX SI1 Clock Route Register (CMXSI1CR)

The CMX SI1 clock route register (CMXSI1CR) deÞnes the connection of SI1 to the clock

sources that can be input from the bank of clocks.

1

0

ÂSAD4

1

0

ÂSAD3

1

0

ÂSAD2

1

0

ÂSAD1

1

0

ÂSAD0

1

0

SAD0

1

0

SAD1

1

0

SAD2

1

0

SAD3

1

0

SAD4

1

0

MAD4

1

0

MAD3

FCC1 Rx Master Address

msb

lsb

FCC1 Rx Slave Address

msb

lsb

FCC2 Rx Slave Address

msb

lsb

FCC2 Rx Master Address

msb

lsb

FCC1-RxAddr[4]

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

FCC1

FCC2

PIO

PA4

PIO

PD18

PIO

PD29

PIO

PC6

PIO

PC12

PIO

PC14

PIO

PA5

PIO

PA3

FCC2-RxAddr[3] (master)

FCC2-RxAddr[0] (slave)

FCC1-RxAddr[3]

FCC2-RxAddr[4] (master)

FCC2-RxAddr[1] (slave)

FCC1-RxAddr[2]

FCC2-RxAddr[2] (slave)

FCC1-RxAddr[1]

FCC2-RxAddr[3] (slave)

FCC1-RxAddr[0]

FCC2-RxAddr[4] (slave)

FCC2-RxAddr[2] (master)

FCC2-RxAddr[1] (master)

FCC2-RxAddr[0] (master)