4 ethernet channel frame transmission, Ethernet channel frame transmission -5, Connecting the mpc8260 to ethernet -5 – Motorola MPC8260 User Manual

Page 879

MOTOROLA

Chapter 30. Fast Ethernet Controller

30-5

Part IV. Communications Processor Module

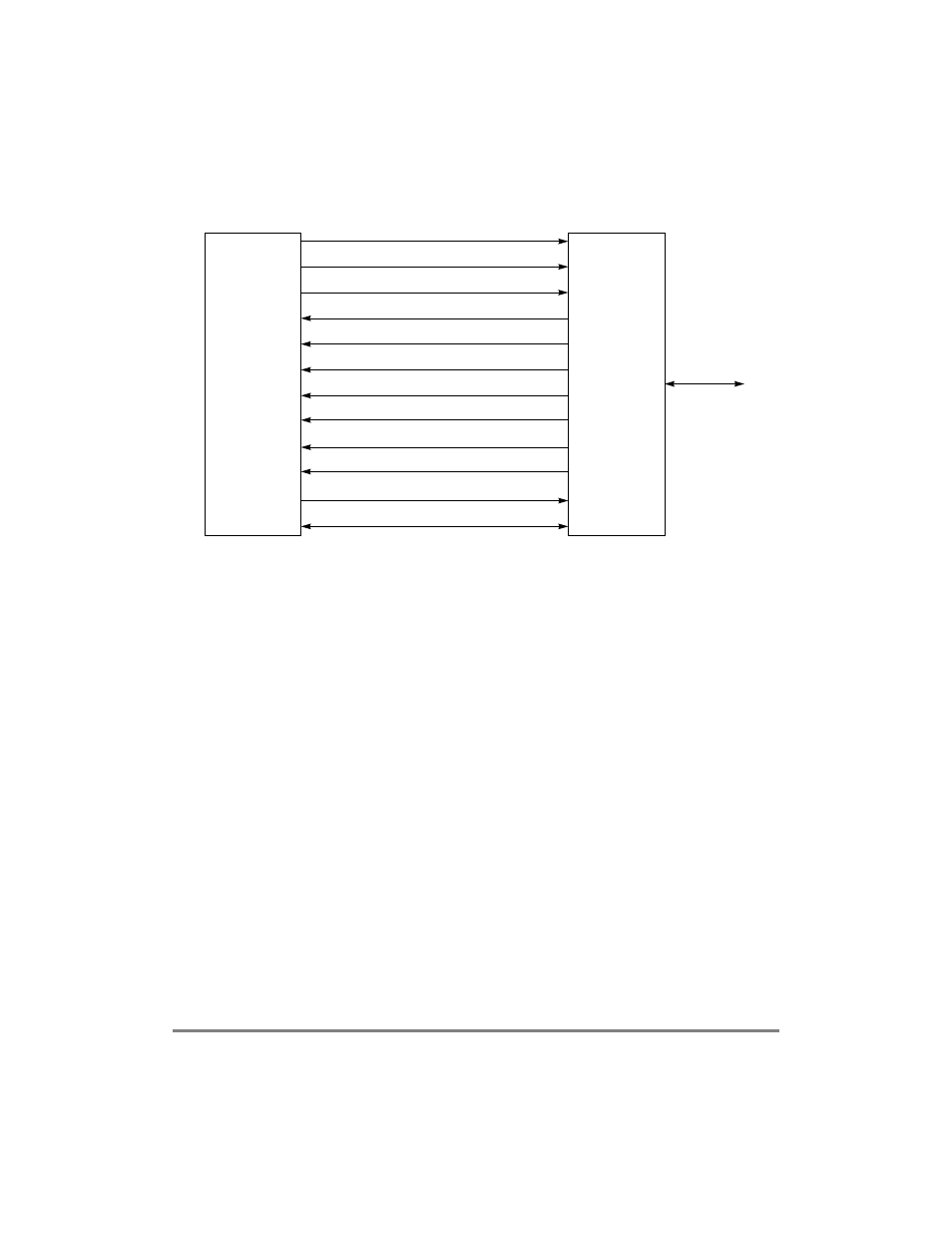

Figure 30-3. Connecting the MPC8260 to Ethernet

Each FCC has 18 signals, deÞned by the IEEE 802.3u standard, for connecting to an

Ethernet PHY. The two management signals (MDC and MDIO) required by the MII should

be implemented separately using the parallel I/O.

The MPC8260 has additional signals for interfacing with an optional external

content-addressable memory (CAM), which are described in Section 30.7, ÒCAM

Interface.Ó

The MPC8260 uses the SDMA channels to store every byte received after the start frame

delimiter into system memory. On transmit, the user provides the destination address,

source address, type/length Þeld, and transmit data. To meet minimum frame requirements,

MPC8260 automatically pads frames with fewer than 64 bytes in the data Þeld. The

MPC8260 also appends the FCS to the frame.

30.4 Ethernet Channel Frame Transmission

The Ethernet transmitter requires almost no core intervention. When the core enables the

transmitter, the Ethernet controller polls the Þrst TxBD in the FCCÕs TxBD table every 256

serial clocks. If the user has a frame ready to transmit, setting TODR[TOD] eliminates

waiting for the next poll. When there is a frame to transmit, the Ethernet controller begins

fetching the data from the data buffer and asserts TX_EN. The preamble sequence, start

Transmit Error (TX_ER)

Transmit Nibble Data 0Ð3 (TXD[0Ð3])

Transmit Enable (TX_EN)

Transmit Clock (TX_CLK)

Collision Detect (COL)

Receive Nibble Data (RXD[0Ð3])

Receive Error (RX_ER)

Receive Clock (RX_CLK)

Receive Data Valid (RX_DV)

Carrier Sense Output (CRS)

Management Data I/O

1

(MDIO)

Management Data Clock

1

(MDC)

MPC8260

Fast Ethernet

PHY

Medium

Media-Independent Interface (MII)

1

The management signals (MDC and MDIO) can be common to all of the Fast Ethernet connections in

the system, assuming that each PHY has a different management address. Use parallel I/O port pins to

implement MDC and MDIO. (The I

2

C controller cannot be used for this function.)