3 60x bus protocol overview, 60x bus protocol overview -4, 60x-compatible bus mode -4 – Motorola MPC8260 User Manual

Page 236

8-4

MPC8260 PowerQUICC II UserÕs Manual

MOTOROLA

Part III. The Hardware Interface

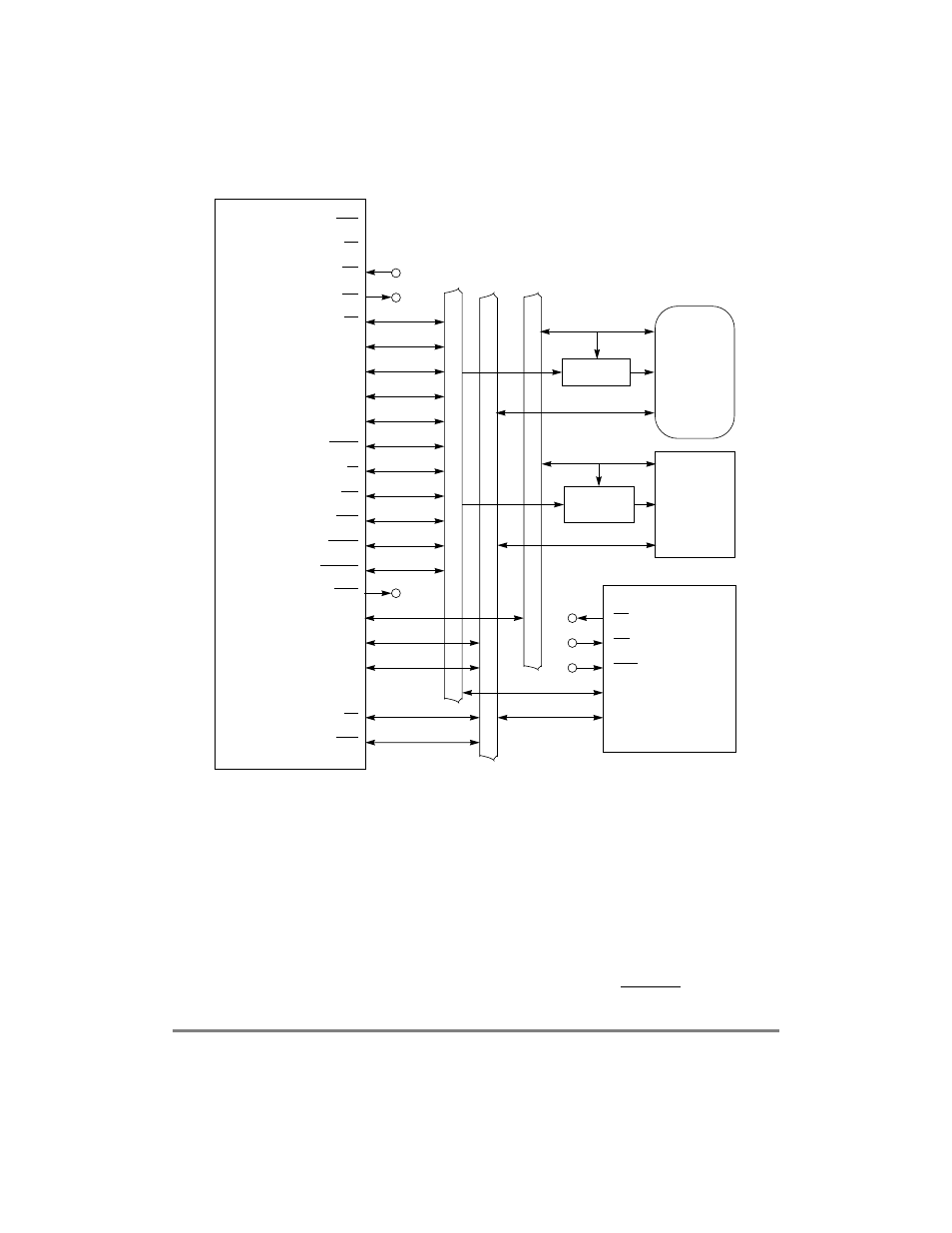

Figure 8-2. 60x-Compatible Bus Mode

8.3 60x Bus Protocol Overview

Typically, 60x bus accesses consist of address and data tenures, which in turn each consist

of three phasesÑarbitration, transfer, and termination, as shown in Figure 8-3 The

independence of the tenures is indicated by showing the data tenure overlap the next

address tenure), which allows split-bus transactions to be implemented at the system level

in multiprocessor systems. Figure 8-3 shows a data transfer that consists of a single-beat

transfer of as many as 256 bits. Four-beat burst transfers of 32-byte cache blocks require

data transfer termination signals for each beat of data. Note that the MPC8260 supports port

sizes of 8, 16, 32, and 64 bits and requires the additional bus signal, PSDVAL, which is not

BR

BG

TS

A[0Ð31]

TT[0Ð4]

TSIZ[0Ð3]

TBST

CI

WT

GBL

AACK

ARTRY

DBG

D[0Ð63]

DP[0Ð7]

TA

TEA

MPC8260

I/O

MEM

Data + Attributes

Address + Attributes

Memory Controller Signals

External Device

BR

BG

DBG

Latch

Latch &

DRAM MUX

Memory Control Signals

AP[0Ð3]

TS

APE