4 programming the spi registers, 1 spi mode register (spmode), Programming the spi registers -6 – Motorola MPC8260 User Manual

Page 930: Spi mode register (spmode) -6, Spmodeñspi mode register -6, Spmode field descriptions -6

33-6

MPC8260 PowerQUICC II UserÕs Manual

MOTOROLA

Part IV. Communications Processor Module

The maximum sustained data rate that the SPI supports is SYSTEMCLK/50. However, the

SPI can transfer a single character at much higher ratesÑSYSTEMCLK/4 in master mode

and SYSTEMCLK/2 in slave mode. Gaps should be inserted between multiple characters

to keep from exceeding the maximum sustained data rate.

33.4 Programming the SPI Registers

The following sections describe the registers used in conÞguring and operating the SPI.

33.4.1 SPI Mode Register (SPMODE)

The SPI mode register (SPMODE), shown in Figure 33-4, controls both the SPI operation

mode and clock source.

Table 33-1 describes the SPMODE Þelds.

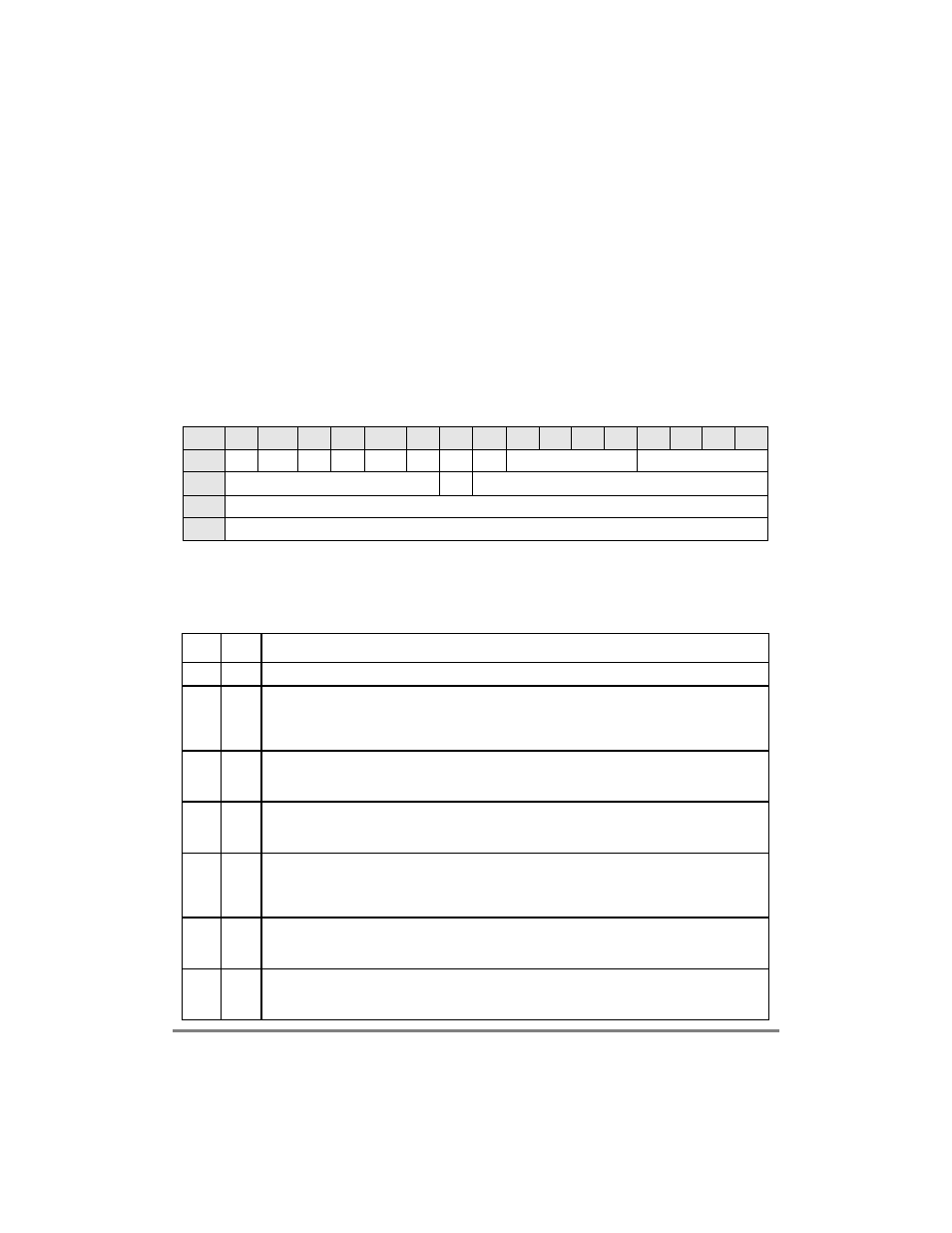

Bit

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

Field

Ñ

LOOP

CI

CP

DIV16

REV

M/S

EN

LEN

PM

Reset

0000_00

—

0_0000_0000

R/W

R/W

Addr

Figure 33-4. SPMODEÑSPI Mode Register

Table 33-1. SPMODE Field Descriptions

Bits

Name

Description

0

Ñ

Reserved, should be cleared.

1

LOOP Loop mode. Enables local loopback operation.

0 Normal operation.

1 Loopback mode. The transmitter output is internally connected to the receiver input. The receiver

and transmitter operate normally, except that received data is ignored.

2

CI

Clock invert. Inverts SPI clock polarity. See Figure 33-5 and Figure 33-6.

0 The inactive state of SPICLK is low.

1 The inactive state of SPICLK is high.

3

CP

Clock phase. Selects the transfer format. See Figure 33-5 and Figure 33-6.

0 SPICLK starts toggling at the middle of the data transfer.

1 SPICLK starts toggling at the beginning of the data transfer.

4

DIV16 Divide by 16. Selects the clock source for the SPI baud rate generator when conÞgured as an SPI

master. In slave mode, SPICLK is the clock source.

0 BRGCLK is the input to the SPI BRG.

1 BRGCLK/16 is the input to the SPI BRG.

5

REV

Reverse data. Determines the receive and transmit character bit order.

0 Reverse dataÑlsb of the character sent and received Þrst.

1 Normal operationÑmsb of the character sent and received Þrst.

6

M/S

Master/slave. Selects master or slave mode.

0 The SPI is a slave.

1 The SPI is a master.