4 local bus sdram mode register (lsdmr), Local bus sdram mode register (lsdmr) -24, Lsdmr field descriptions -24 – Motorola MPC8260 User Manual

Page 300: Section 10.3.4, Able 10-8

10-24

MPC8260 PowerQUICC II UserÕs Manual

MOTOROLA

Part III. The Hardware Interface

10.3.4 Local Bus SDRAM Mode Register (LSDMR)

The LSDMR, shown in Figure 10-10, has the same Þelds as the PSDMR. Table 10-8

describes LSDMR Þelds.

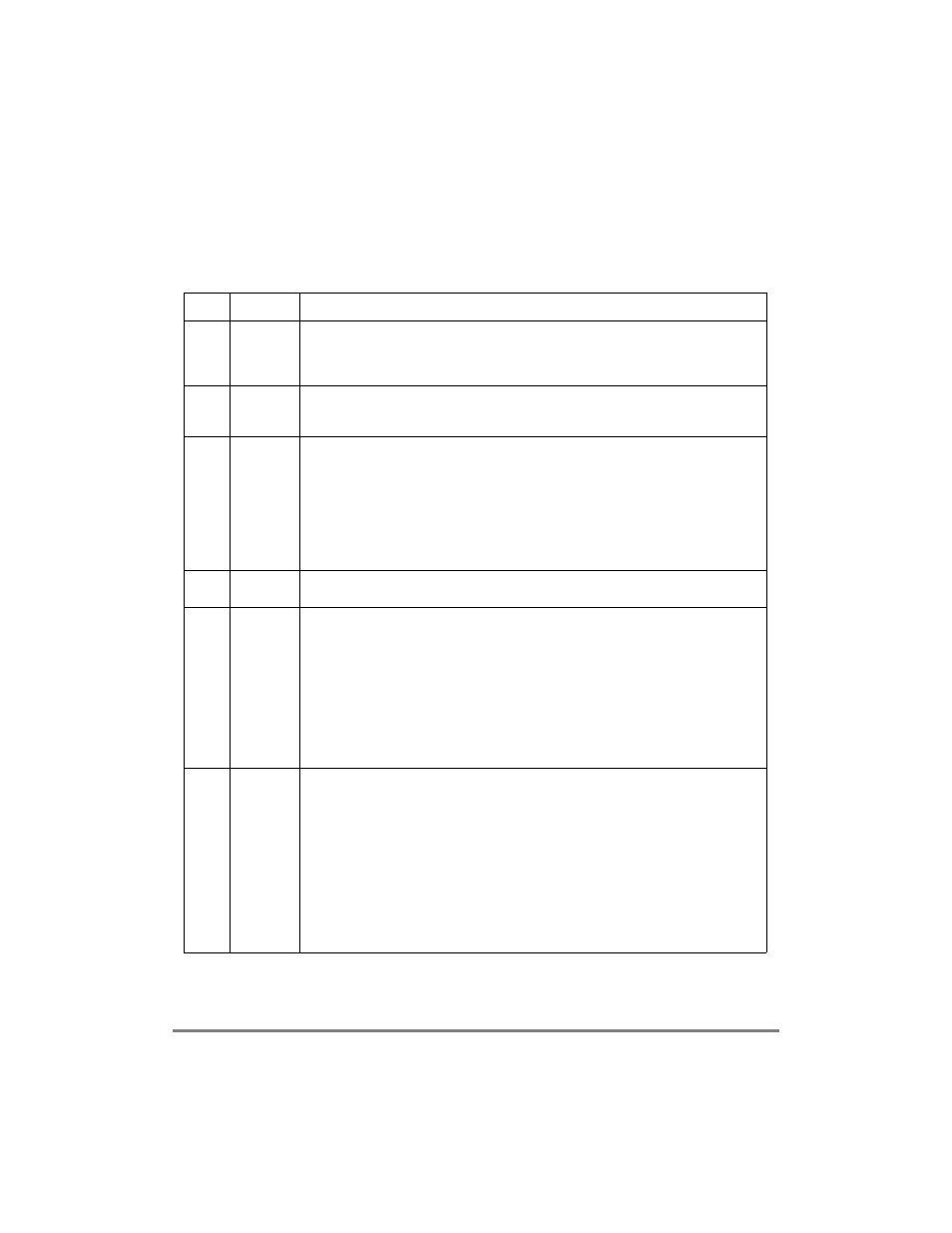

Table 10-8. LSDMR Field Descriptions

Bits

Name

Description

0

PBI

Page-based interleaving. Selects the address multiplexing method. PBI works in conjunction

with ORx[SDA10]. See Section 10.4.5, ÒBank Interleaving.Ó

0 Bank-based interleaving

1 Page-based interleaving (normal operation)

1

RFEN

Refresh enable. Indicates that the SDRAM requires refresh services.

0 Refresh services are not required

1 Refresh services are required

2Ð4

OP

SDRAM operation. Selects the operation that occurs when the SDRAM device is accessed.

000 Normal operation

001 CBR refresh, used in SDRAM initialization.

010 Self refresh (for debug purpose).

011 Mode Register write, used in SDRAM initialization.

100 Precharge bank (for debug purpose).

101 Precharge all banks, used in SDRAM initialization.

110 Activate bank (for debug purpose).

111 Read/write (for debug purpose).

5Ð7

SDAM

Address multiplex size. Determines how the address of the current memory cycle is output on

the address pins. See Section 10.4.5.1, ÒSDRAM Address Multiplexing (SDAM and BSMA).У

8Р10

BSMA

Bank select multiplexed address line. Selects which MPC8260 address pins serve as

bank-select address for the local bus SDRAM. See Section 10.4.5.1, ÒSDRAM Address

Multiplexing (SDAM and BSMA).Ó

000 L_A14 (ORx[BPD] must be 00)

001 L_AÐL_A15 (ORx[BPD] must be 00 or 01)

010 L_A14ÐL_A16

011 L_A15ÐL_A17

100 L_A16ÐL_A18

101 L_A17ÐL_A19

110 L_A18ÐL_A20

111 L_A19ÐL_A21

11Ð13

SDA10

ТA10У control. When SDRAM is selected, with ORx[PBI], determines which address line is

output to SDA10 during an

ACTIVATE

command, to control the memory access. See

Section 10.4.12.1, ÒSDRAM ConÞguration Example (Page-Based Interleaving).Ó

For PBI=0:

000 A12

001 A11

010 A10

011 A9

100 A8

101 A7

110 A6

111 A5

For PBI=1:

000 A10

001 A9

010 A8

011 A7

100 A6

101 A5

110 A4

111 A3