Channel mode register (chamr)ñtransparent mode -14, Chamr field descriptionsñtransparent mode -14, Figure 27-10 sho – Motorola MPC8260 User Manual

Page 744: Chamr þelds are described in table 27-5

27-14

MPC8260 PowerQUICC II UserÕs Manual

MOTOROLA

Part IV. Communications Processor Module

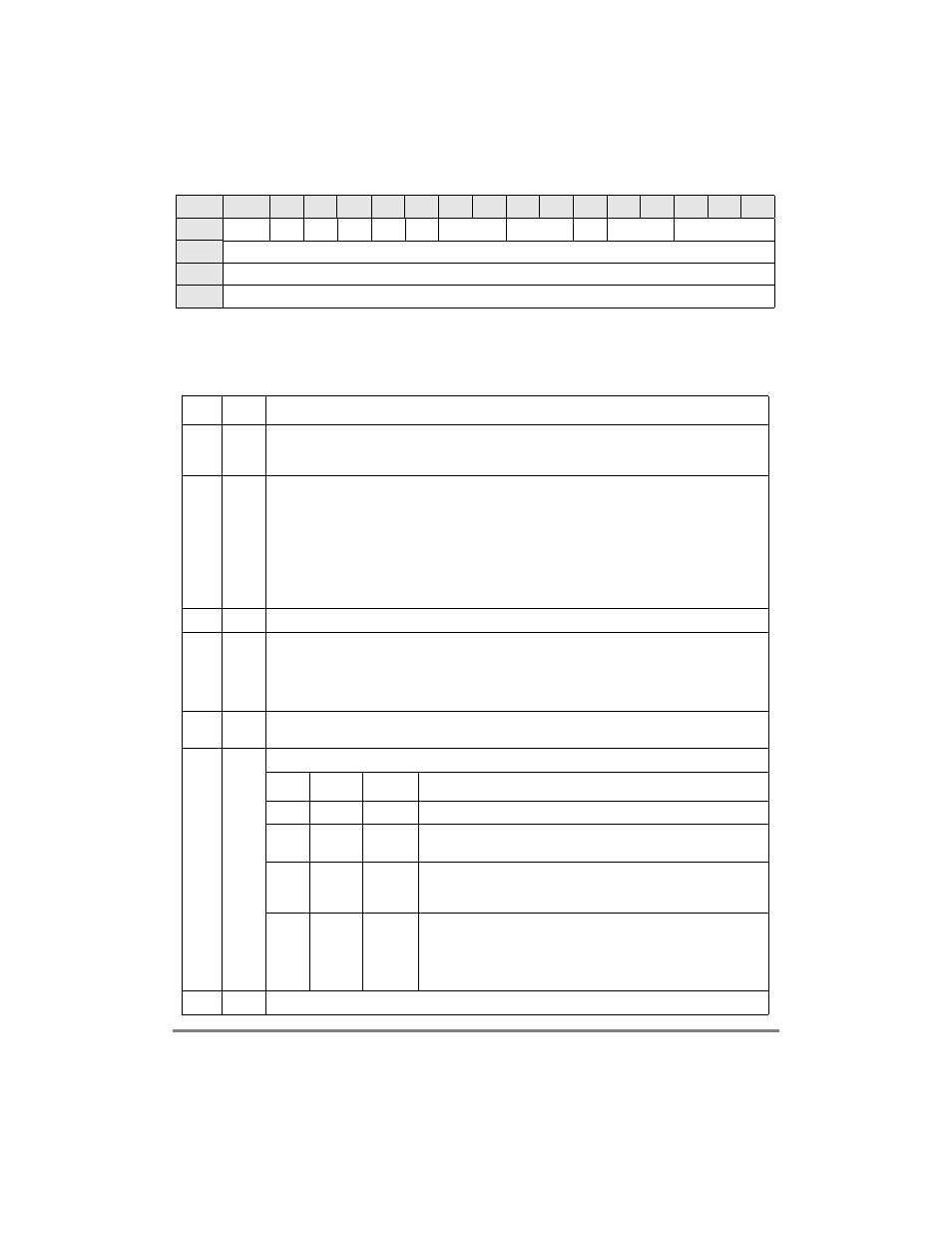

CHAMR Þelds are described in Table 27-5,

Bits

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

Field

MODE

POL

1

1

EP

RD

SYNC

Ñ

TS

RQN

Ñ

Reset

Ñ

R/W

R/W

Offset

0x1A

Figure 27-10. Channel Mode Register (CHAMR)ÑTransparent Mode

Table 27-8. CHAMR Field DescriptionsÑTransparent Mode

Bits Name

Description

0

MODE

Channel mode. Selects either HDLC or transparent mode.

0 Transparent mode.

1 HDLC mode

1

POL

Enable polling. POL enables the transmitter to poll the TxBDs.

0 Polling is disabled (The CPM does not access the external bus to check the R bit in the TxBD).

1 Polling is enabled.

POL can be used to optimize the use of the external bus. Software should always set POL at the

beginning of a transmit sequence of one or more frames. The CP clears POL when no more buffers

are ready in the transmit queue, i.e. when it Þnds a BD with R = 0 (for example, at the end of a frame

or at the end of a multi-frame transmission). To prevent a signiÞcant number of useless transactions

on the external bus, software should always prepare the new BD, or multiple BDs, and set BD[R]

before enabling polling.

2Ð3

0b11

Must be set.

4

EP

Empty polarity and enable polling.

0 The E bit in the RxBD is handled in positive logic (1 = empty; 0 = not empty). Polling occurs only if

POL is set.

1 The E bit in the RxBD is handled in negative logic (0 = empty, 1 = not empty). Polling occurs

disregarding the value of POL.

5

RD

0 Normal bit order (transmit/receive the lsb of each octet Þrst)

1 Reversed bit order to be reversed (transmit/receive the msb of each octet Þrst).

6Ð7

SYNC

Synchronization. SYNC controls synchronization of multi-channel operation in transparent mode.

SYNC

Receive Transmit

Description

00

None

None

Transmitter and receiver operate with no synchronization algorithm

01

Slot

Slot

The Þrst data is sent/received in the slot deÞned in the slot

assignment table (for super channels only)

10

8-bit

None

Receive data synchronization uses an 8-bit pattern speciÞed by the 8

MSB of RCVSYNC. The sync bytes will not be written to the receive

buffer

11

16-bit

None

Receive data synchronization uses a 16-bit pattern speciÞed by

RCVSYNC. The Þrst byte of the sync pattern will not be written to the

receive buffer. The second byte of the sync pattern will be written to

the receive buffer (Þrst and second represent the order in which the

two bytes of the sync pattern are received on the serial channel).

8Р9

С

Reserved, must be cleared.