3 programming model, 1 interrupt controller registers, 1 siu interrupt configuration register (sicr) – Motorola MPC8260 User Manual

Page 155: Programming model -17, Interrupt controller registers -17, Siu interrupt configuration register (sicr) -17, 1 siu interrupt conþguration register (sicr)

MOTOROLA

Chapter 4. System Interface Unit (SIU)

4-17

Part II. ConÞguration and Reset

4.3 Programming Model

The SIU registers are grouped into the following three categories:

¥

Interrupt controller registers. These registers control conÞguration, prioritization,

and masking of interrupts. They also include registers for determining the interrupt

sources. These registers are described in Section 4.3.1, ÒInterrupt Controller

Registers.Ó

¥

System conÞguration and protection registers. These include registers for

conÞguring the SIU, deÞning the base address for the internal memory map,

conÞguring the watchdog timer, specifying bus characteristics, as well as general

functionality of the 60x, and local buses such as arbitration, error status, and control.

These registers are described in Section 4.3.2, ÒSystem ConÞguration and

Protection Registers.Ó

¥

Periodic interrupt registers. These include registers for conÞguring and providing

status for periodic interrupts. See Section 4.3.3, ÒPeriodic Interrupt Registers.Ó

4.3.1 Interrupt Controller Registers

There are seven interrupt controller registers, described in the following sections:

¥

Section 4.3.1.1, ÒSIU Interrupt ConÞguration Register (SICR)Ó

¥

Section 4.3.1.2, ÒSIU Interrupt Priority Register (SIPRR)Ó

¥

Section 4.3.1.3, ÒCPM Interrupt Priority Registers (SCPRR_H and SCPRR_L)Ó

¥

Section 4.3.1.4, ÒSIU Interrupt Pending Registers (SIPNR_H and SIPNR_L)Ó

¥

Section 4.3.1.5, ÒSIU Interrupt Mask Registers (SIMR_H and SIMR_L)Ó

¥

Section 4.3.1.6, ÒSIU Interrupt Vector Register (SIVEC)Ó

¥

Section 4.3.1.7, ÒSIU External Interrupt Control Register (SIEXR)Ó

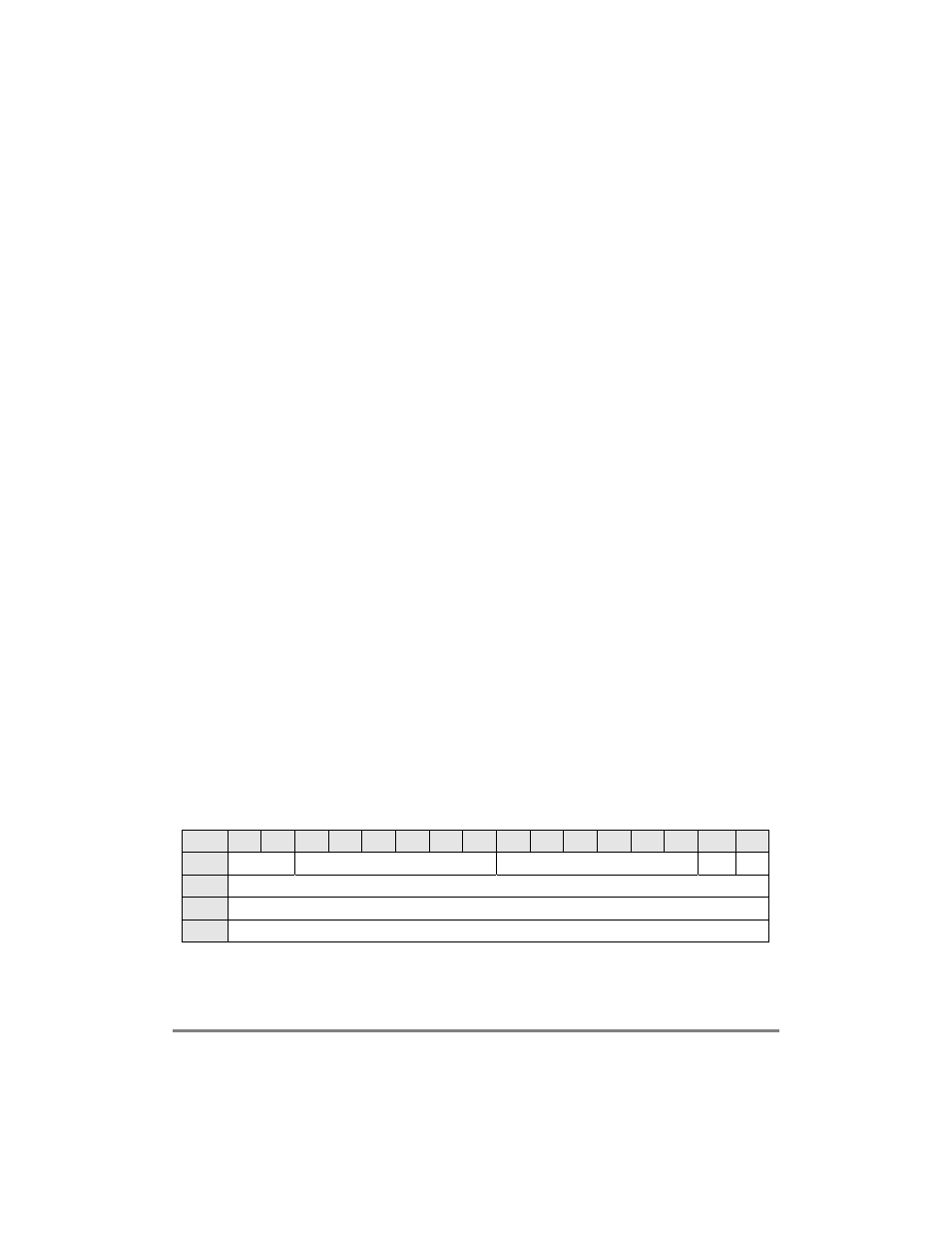

4.3.1.1 SIU Interrupt ConÞguration Register (SICR)

The SIU interrupt conÞguration register (SICR), shown in Figure 4-10, deÞnes the highest

priority interrupt and whether interrupts are grouped or spread in the priority table,

Table 4-2.

Bits

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

Field

Ñ

HP

Ñ

GSIU

SPS

Reset

0000_0000_0000_0000

R/W

R/W

Addr

Figure 4-10. SIU Interrupt Configuration Register (SICR)