Motorola MPC8260 User Manual

Page 488

14-34

MPC8260 PowerQUICC II UserÕs Manual

MOTOROLA

Part IV. Communications Processor Module

For example, assuming that SCC1 is connected to the D channel, SCC2 to the B1 channel,

and SMC2 to the B2 channel, SMC1 is used to handle the C/I channels, and the D-channel

grant is on bit 4 of the C/I on SCIT channel 2, the initialization sequence is as follows:

1. Program both the Tx and Rx sections of the SIx RAM as in Table 14-12 beginning

at addresses 0 and 1024, respectively.

2. SI1AMR = 0x00c0. TDMa is used in double speed clock and common Rx/Tx

modes. SCIT mode is used in this example.

Note: If SCIT mode is not used, delete the last three entries of

the SIx RAM, divide one entry into two and set the LST bit in

the new last entry.

3. CMXSMR = 0x88. SMC1 and SMC2 are connected to the TSA.

4. CMXSCR = 0xC040_0000. SCC2 and SCC1 are connected to the TSA. SCC1

supports the grant mechanism since it is on the D channel.

5. CMXSI1CR = 0x00. TDMa uses CLK1.

6. Set PPARA[6Ð9]. ConÞgures L1TXDa[0], L1RXDa[0], L1TSYNCa and

L1RSYNCa.

7. Set PSORA[6Ð9]. ConÞgures L1TXDa[0], L1RXDa[0], L1TSYNCa and

L1RSYNCa.

8. Set PDIRA[9]. ConÞgures L1TXDa[0].

9. Set PODRA[9]. ConÞgures L1TXDa[0] to an open-drain output.

10. Set PPARC[30,31]. ConÞgures L1TCLKa and L1RCLKa.

11. Clear PDIRC[30,31]. ConÞgures L1TCLKa and L1RCLKa.

12. Clear PSORC[30,31]. ConÞgures L1TCLKa and L1RCLKa.

13. Set PPARB[17]. ConÞgures L1CLKO and L1RQa.

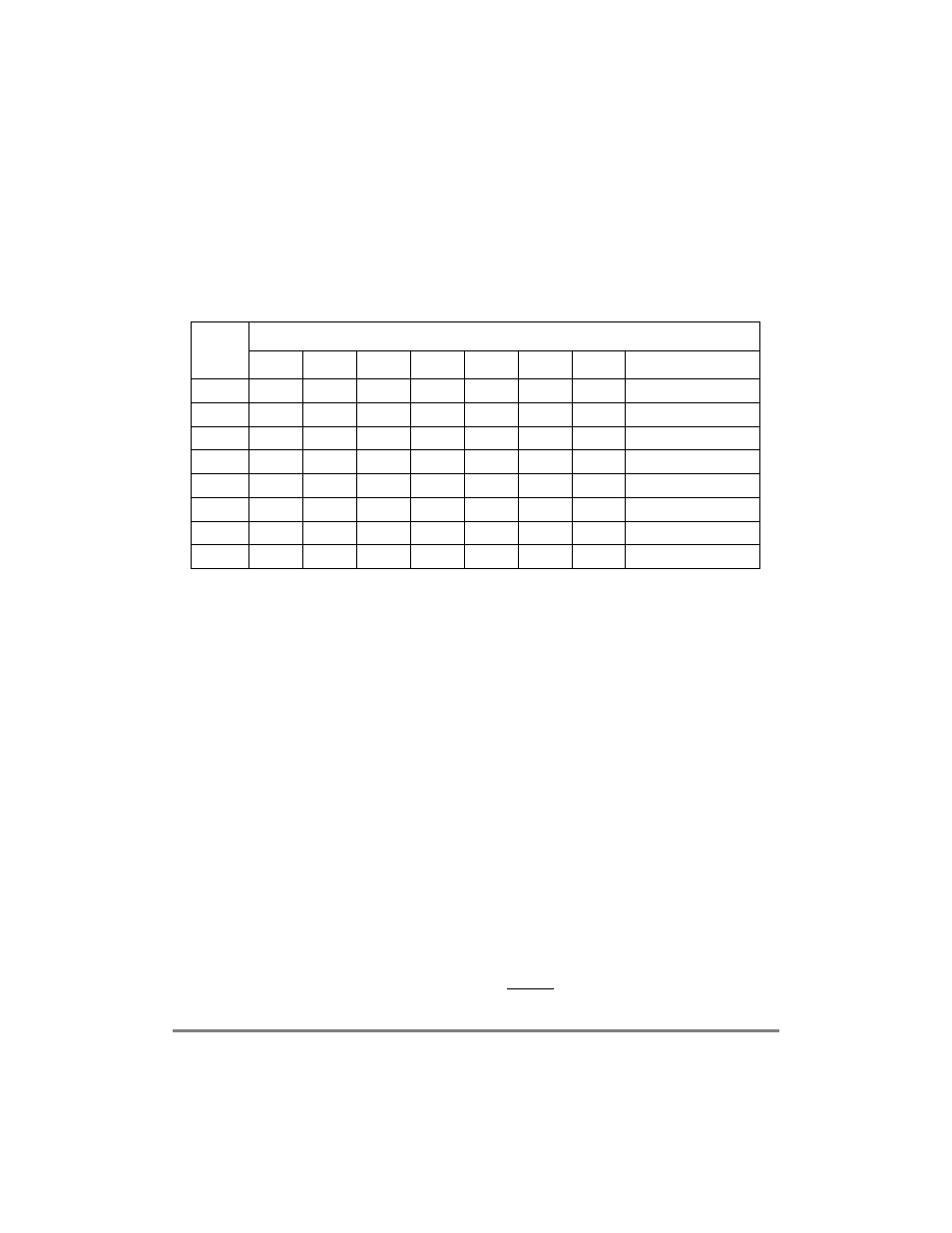

Table 14-12. SIx RAM Entries for a GCI Interface (SCIT Mode)

Entry

Number

SIx RAM Entry

MCC

SWTR

SSEL

CSEL

CNT

BYT

LST

Description

0

0

0

0000

0010

000

1

0

8 Bits SCC2

1

0

0

0000

0110

000

1

0

8 Bits SMC2

2

0

0

0000

0101

000

1

0

8 Bits SMC1

3

0

0

0000

0001

001

0

0

2 Bits SCC1

4

0

0

0000

0101

101

0

0

6 Bits SMC1

5

0

0

0000

0000

110

1

0

Skip 7 bytes

6

0

0

0000

0000

001

0

0

Skip 2 bits

7

0

0

0000

0111

000

0

1

D grant bit