3 channel mode register (chamr), Channel mode register (chamr) -10, Intmsk mask bits -10 – Motorola MPC8260 User Manual

Page 740: Chamr field descriptions -10, See section 27.6.3, òchannel mode register (chamr)

27-10

MPC8260 PowerQUICC II UserÕs Manual

MOTOROLA

Part IV. Communications Processor Module

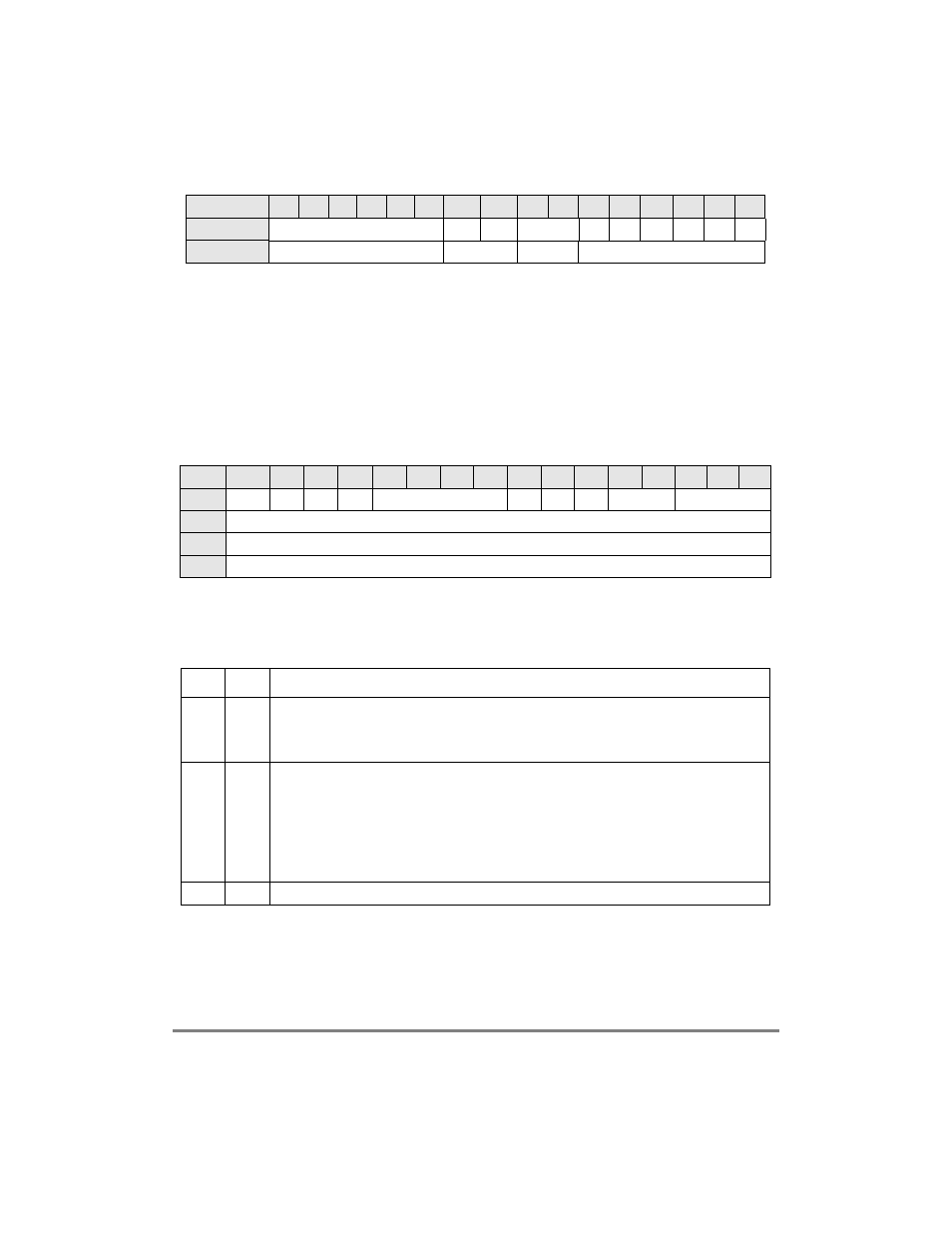

To enable an interrupt, set the corresponding bit. If a bit is cleared, no interrupt request is

generated and no new entry is written in the circular interrupt table. The user must initialize

INTMSK prior to operation. Reserved bits are cleared.

27.6.3 Channel Mode Register (CHAMR)

The channel mode register (CHAMR) is a user-initialized register, shown in Figure 27-8.

This is a generalized representation of CHAMR. Section 27.7.1, ÒChannel Mode Register

(CHAMR)ÑTransparent Mode,Ó describes the CHAMR for transparent mode.

CHAMR Þelds are described in Table 27-5.

Bits

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

Interrupt Entry

Ñ

UN

TXB

Ñ

NID

IDL

MRF RXF BSY RXB

INTMSK

Ñ

Mask Bits

Ñ

Mask Bits

Figure 27-7. INTMSK Mask Bits

Bits

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

Field

MODE

POL

1

IDLM

Ñ

CRC

Ñ

TS

RQN

NOF

Reset

Ñ

R/W

R/W

Offset

0x1A

Figure 27-8. Channel Mode Register (CHAMR)

Table 27-5. CHAMR Field Descriptions

Bits

Name Description

0

MODE

This mode bit determines whether the HDLC or transparent mode is used. It also determines how

other CHAMR bits are interpreted.

0 Transparent mode. See Section 27.7.1, ÒChannel Mode Register (CHAMR)ÑTransparent Mode.Ó

1 HDLC mode

1

POL

Enable polling. POL enables the transmitter to poll the TxBDs.

0 Polling is disabled (The CPM does not access the external bus to check the R bit in the TxBD).

1 Polling is enabled.

POL can be used to optimize the use of the external bus. Software should always set POL at the

beginning of a transmit sequence of one or more frames. The CP clears POL when no more buffers

are ready in the transmit queue, i.e. when it Þnds a BD with R = 0 (for example, at the end of a frame

or at the end of a multi-frame transmission). To minimize useless transactions on the external bus,

software should always prepare the new BD, or multiple BDs, and set BD[R] before enabling polling.

2

1

Must be set.