Scc hdlc interrupt event example -13 – Motorola MPC8260 User Manual

Page 621

MOTOROLA

Chapter 21. SCC HDLC Mode

21-13

Part IV. Communications Processor Module

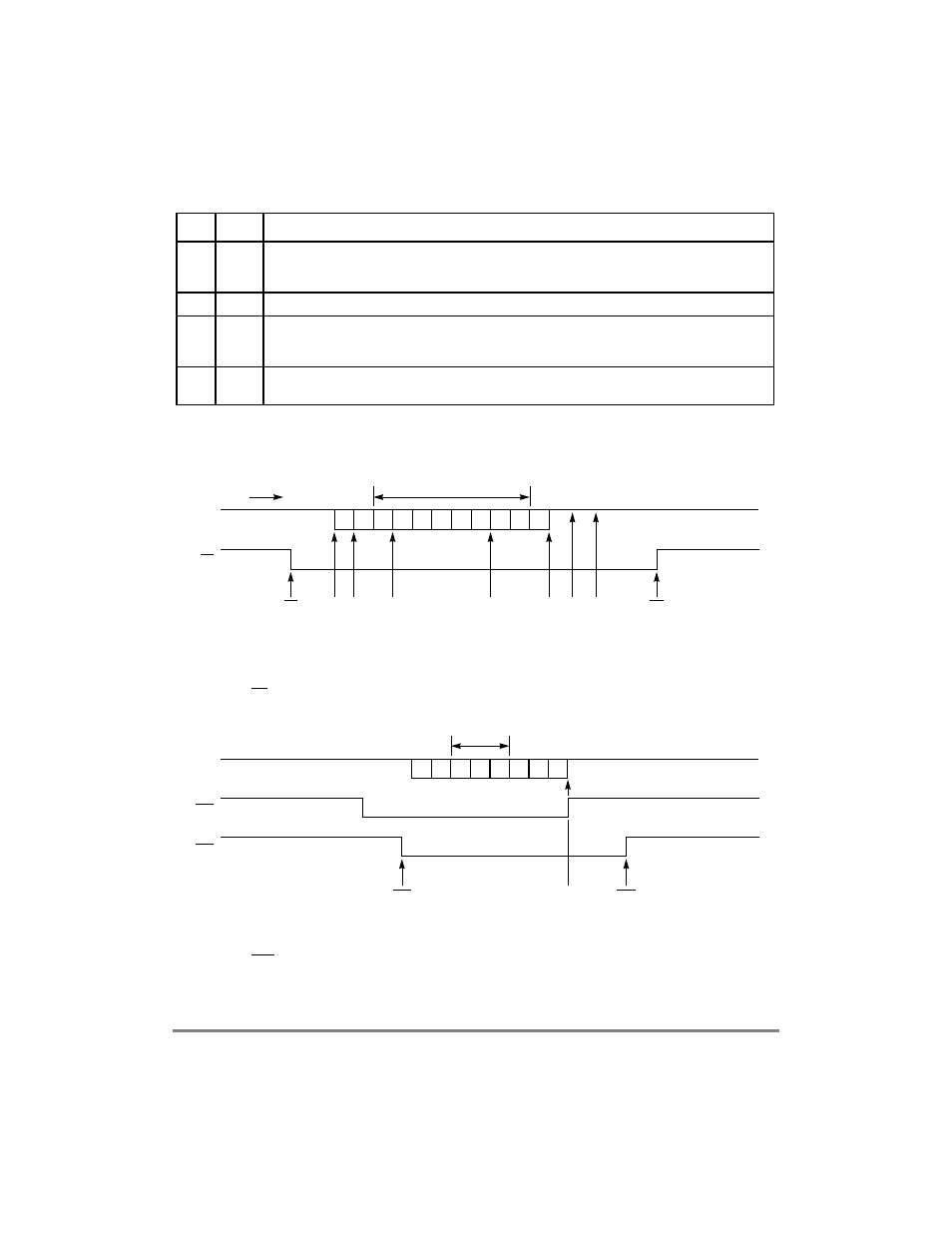

Figure 21-8 shows interrupts that can be generated using the HDLC protocol.

Figure 21-8. SCC HDLC Interrupt Event Example

12

RXF

Rx frame. Set when the number of receive frames speciÞed in RFTHR are received on the HDLC

channel. It is set no sooner than two clocks after the last bit of the closing ßag is received. This event is

not maskable via the RxBD[I] bit.

13

BSY

Busy condition. Indicates a frame arrived but was discarded due to a lack of buffers.

14

TXB

Transmit buffer. Enabled by setting TxBD[I]. TXB is set when a buffer is sent on the HDLC channel. For

the last buffer in the frame, TXB is not set before the last bit of the closing ßag begins its transmission;

otherwise, it is set after the last byte of the buffer is written to the Tx FIFO.

15

RXB

Receive buffer. Enabled by setting RxBD[I]. RXB is set when the HDLC channel receives a buffer that

is not the last in a frame.

Table 21-9. SCCE/SCCM Field Descriptions (Continued)

Bits

Name

Description

CD

IDL

FLG

RXB

RXF

IDL

CD

Line Idle

Stored in Rx Buffer

RXD

CD

Frame

Received by HDLC

Time

Line Idle

TXD

RTS

Frame

Transmitted by HDLC

CTS

TXB

CTS

CTS

Line Idle

Line Idle

Stored in Tx Buffer

NOTES

:

HDLC SCCE

Events

1. RXB event assumes receive buffers are 6 bytes each.

2. The second IDL event occurs after 15 ones are received in a row.

3. The FLG interrupts show the beginning and end of flag reception.

4. The FLG interrupt at the end of the frame may precede the RXF interrupt due to receive FIFO latency.

5. The CD event must be programmed in the port C parallel I/O, not in the SCC itself.

NOTES:

HDLC SCCE

Events

1. TXB event shown assumes all three bytes were put into a single buffer.

2. Example shows one additional opening flag. This is programmable.

F

F

A

A

C

I

I

I

CR CR F

FLG

FLG

FLG

6. F = flag, A = address byte, C = control byte, I = information byte, and CR = CRC byte

F

F

A

A

C CR CR F

3. The CTS event must be programmed in the port C parallel I/O, not in the SCC itself.