4 free buffer pool parameter tables, Free buffer pool parameter tables -68, Free buffer pool entry -68 – Motorola MPC8260 User Manual

Page 848: Free buffer pool entry field descriptions -68, Free buffer pool parameter table -68

29-68

MPC8260 PowerQUICC II UserÕs Manual

MOTOROLA

Part IV. Communications Processor Module

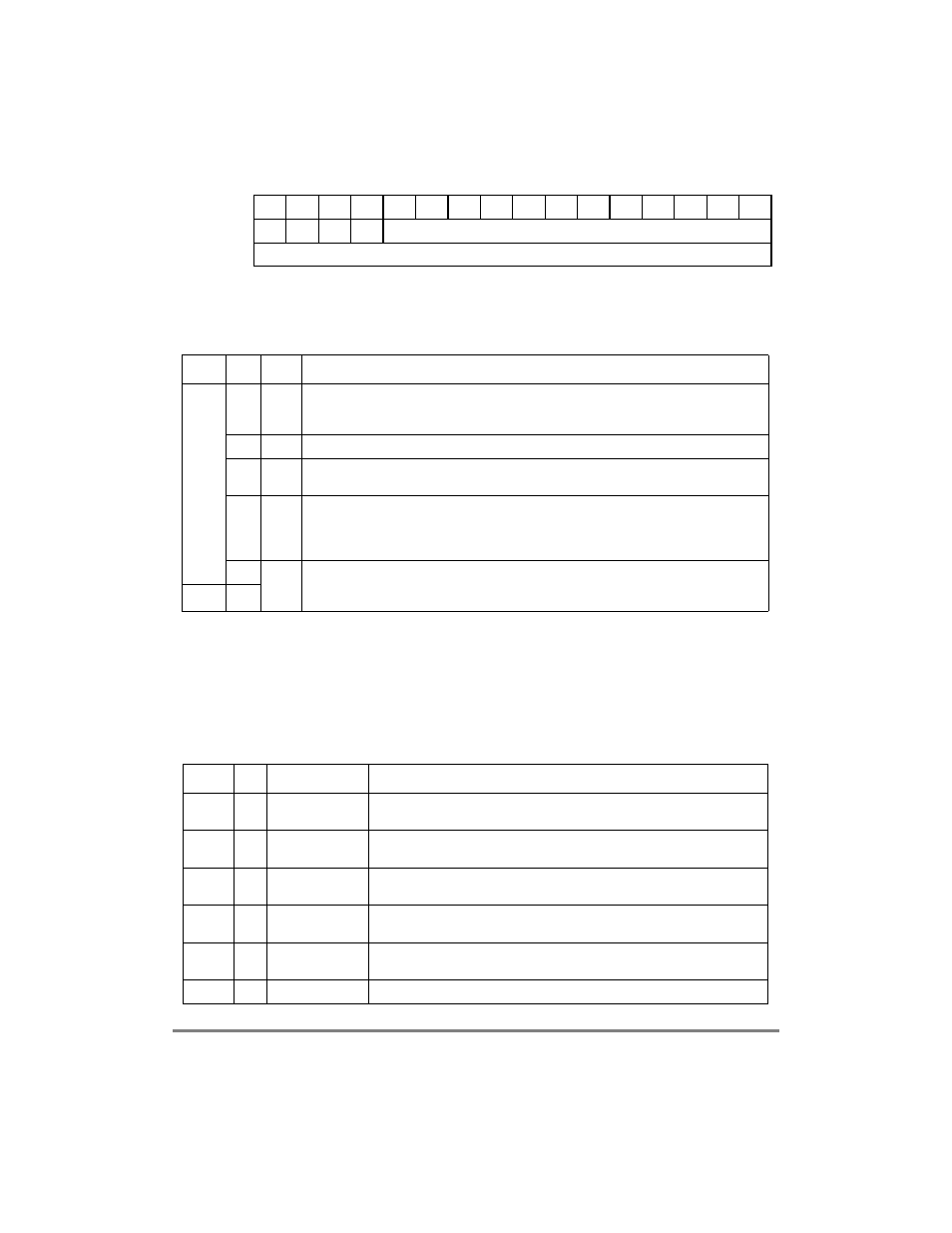

Table 29-32 describes free buffer pool entry Þelds.

29.10.5.2.4 Free Buffer Pool Parameter Tables

The free buffer pool parameters are held in parameter tables in the dual-port RAM; see

Table 29-33. FBT_BASE in the parameter RAM points to the base address of these tables.

Each of the four free buffer pools has its own parameter table with a starting address given

by FBT_BASE+ RCT[BPOOL]

´ 16.

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

Offset + 0x00

V

Ñ

W

I

Buffer Pointer (BP)

Offset + 0x02

Buffer Pointer (BP)

Figure 29-45. Free Buffer Pool Entry

Table 29-32. Free Buffer Pool Entry Field Descriptions

Offset

Bits

Name

Description

0x00

0

V

Valid buffer entry.

0 This free buffer pool entry contains an invalid buffer pointer.

1 This free buffer pool entry contains a valid buffer pointer.

1

Ñ

Reserved, should be cleared.

2

W

Wrap bit. When set, this bit indicates the last entry in the circular table. During initialization,

the host must clear all W bits in the table except the last one, which must be set.

3

I

Red-line interrupt. Can be used to indicate that the free buffer pool has reached a red line and

additional buffers should be added to this pool to avoid a busy condition.

0 No interrupt is generated.

1 A red-line interrupt is generated when this buffer is fetched from the free buffer pool.

4Ð15

BP

Buffer pointer. Points to the start address of the receive buffer. The four msbs are control bits,

and the four msbs of the real buffer pointer are taken from the four msbs of the parameter

FBP_ENTRY_EXT in the free buffer pool parameter table.

0x02

0Ð15

Table 29-33. Free Buffer Pool Parameter Table

Offset

1

Bits

Name

Description

0x00

Ñ

FBP_BASE

Free buffer pool base. Holds the pointer to the Þrst entry in the free buffer pool.

FBP_BASE should be word aligned. User-deÞned.

0x04

Ñ

FBP_PTR

Free buffer pool pointer. Pointer to the current entry in the free buffer pool.

Initialize to FBP_BASE.

0x08

Ñ

FBP_ENTRY_EXT Free buffer pool entry extension. FBP_ENTRY_EXT[0Ð3] holds the four left bits

of FBP_ENTRY. FBP_ENTRY_EXT[4Ð15] should be cleared. User-deÞned.

0x0A

0

BUSY

The CP sets this bit when it tries to fetch buffer pointer with V bit clear.

FCCE[GBPB] is also set. Initialize to zero.

1

RLI

Red-line interrupt. Set by the CP when it fetches a buffer pointer with I = 1.

FCCE[GRLI] is also set. Initialize to zero.

2Р7

С

Reserved, should be cleared.