2 data bus parity (dp[0–7])—input, 8 data transfer termination signals, 1 transfer acknowledge (ta) – Motorola MPC8260 User Manual

Page 229: 1 transfer acknowledge (ta)—input, Data bus parity (dp[0ð7])ñinput -15, Data transfer termination signals -15, Transfer acknowledge (ta) -15, Transfer acknowledge (ta)ñinput -15, Dp[0ð7] signal assignments -15

MOTOROLA

Chapter 7. 60x Signals

7-15

Part III. The Hardware Interface

Timing Comments

Assertion/NegationÑThe same as the data bus.

High ImpedanceÑThe same as the data bus.

7.2.7.2.2 Data Bus Parity (DP[0Ð7])ÑInput

Following are the state meaning and timing comments for the DP input signals.

State Meaning

Asserted/NegatedÑRepresents odd parity for each byte of read data.

Parity is checked on all data byte lanes, regardless of the size of the

transfer. Detected even parity causes a checkstop if data parity errors

are enabled in the BCS[PAR_EN].

Timing Comments

Assertion/NegationÑThe same as D[0Ð63].

7.2.8 Data Transfer Termination Signals

Data termination signals are required after each data beat in a data transfer. Note that in a

single-beat transaction that is not a port-size transfer, the data termination signals also

indicate the end of the tenure. In burst or port size accesses, the data termination signals

apply to individual beats and indicate the end of the tenure only after the Þnal data beat. For

a detailed description of how these signals interact, see Section 8.5, ÒData Tenure

Operations.Ó

7.2.8.1 Transfer Acknowledge (TA)

The transfer acknowledge (TA) signal is both input and output on the MPC8260.

7.2.8.1.1 Transfer Acknowledge (TA)ÑInput

Following are the state meaning and timing comments for the TA input signal.

State Meaning

AssertedÑIndicates that a single-beat data transfer completed

successfully or that a data beat in a burst transfer completed

successfully. Note that TA must be asserted for each data beat in a

burst transaction. For more information, see Section 8.5.3, ÒData

Bus Transfers and Normal Termination.Ó

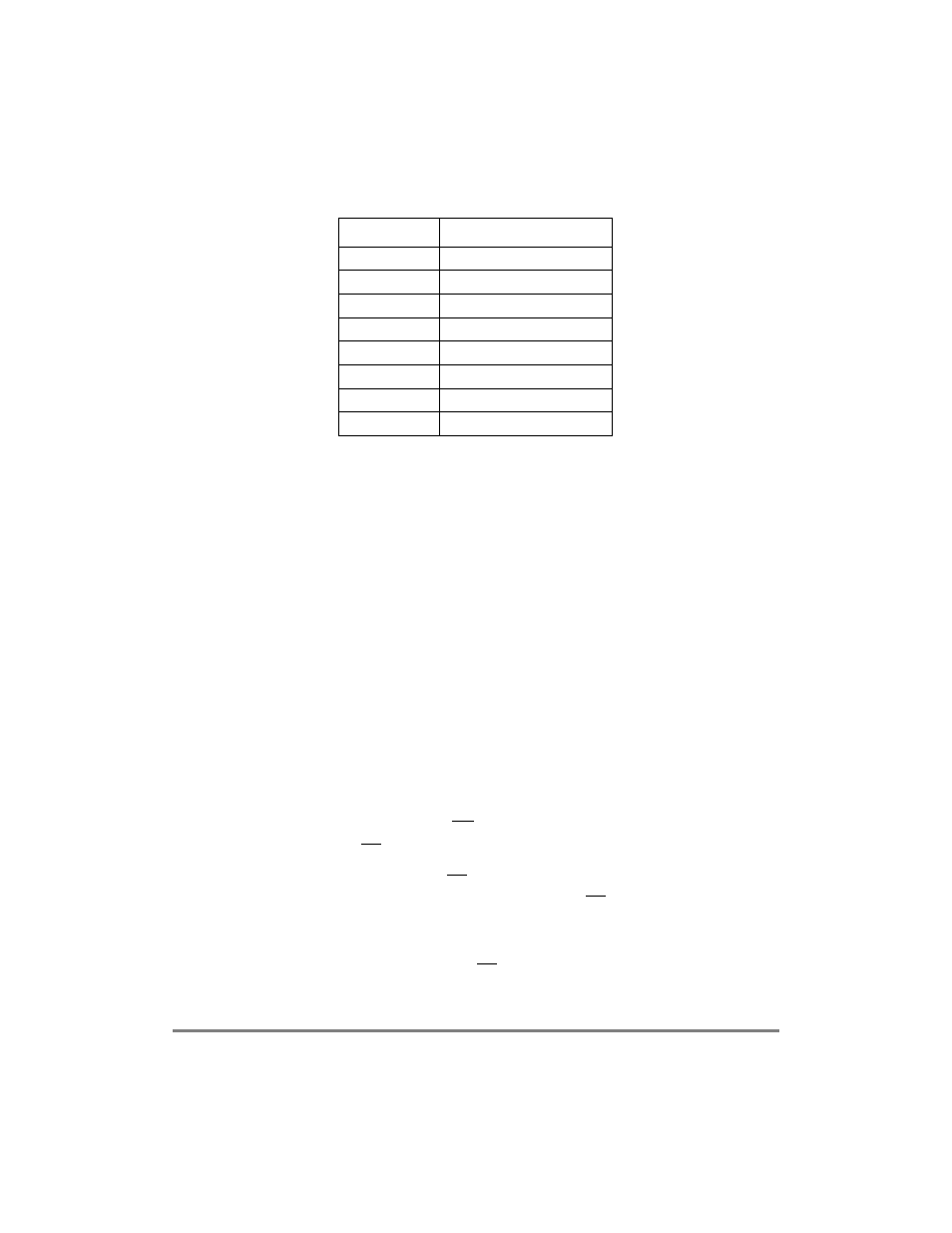

Table 7-1. DP[0Ð7] Signal Assignments

Signal Name

Data Bus Signal Assignments

DP0

D[0Ð7]

DP1

D[8Ð15

DP2

D[16Ð23]

DP3

D[24Ð31]

DP4

D[32Ð39]

DP5

D[40Ð47]

DP6

D[48Ð55]

DP7

D[56Р63]