6 aal0 rxbd, Aal0 rxbd -72, Aal1 rxbd field descriptions -72 – Motorola MPC8260 User Manual

Page 852

29-72

MPC8260 PowerQUICC II UserÕs Manual

MOTOROLA

Part IV. Communications Processor Module

Table 29-36 describes AAL1 RxBD Þelds.

29.10.5.6 AAL0 RxBD

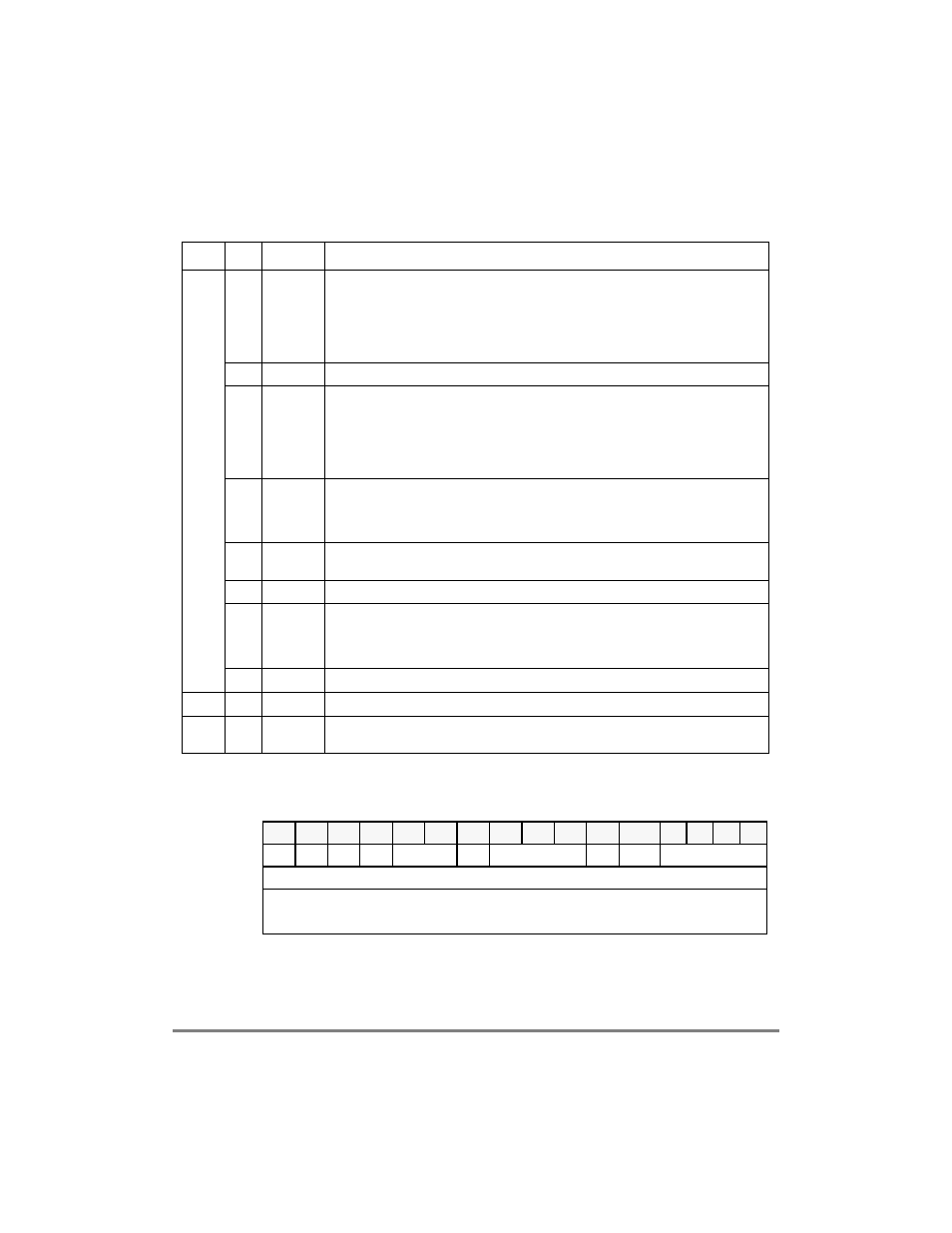

Figure 29-48 shows the AAL0 RxBD.

Table 29-36. AAL1 RxBD Field Descriptions

Offset

Bits

Name

Description

0x00

0

E

Empty

0 The buffer associated with this RxBD is Þlled with received data or data reception was

aborted due to an error. The core can read or write any Þelds of this RxBD. The CP

cannot use this BD again while E = 0.

1 The buffer is not full. This RxBD and its associated receive buffer are owned by the CP.

Once E is set, the core should not write any Þelds of this RxBD.

1

Ñ

Reserved, should be cleared.

2

W

Wrap (Þnal BD in table)

0 This is not the last BD in the RxBD table of the current channel.

1 This is the last BD in the RxBD table of this current channel. After this buffer is used,

the CP receives incoming data into the Þrst BD in the table. The number of RxBDs in

this table is programmable and is determined only by the W bit. The current table

overall space is constrained to 64 Kbytes.

3

I

Interrupt

0 No interrupt is generated after this buffer has been used.

1 An Rx buffer event is sent to the interrupt queue after the ATM controller uses this

buffer. FCCE[GINTx] is set when the INT_CNT reaches the global interrupt threshold.

4

SNE

Sequence number error. SNE is set when a sequence number error is detected in the

current AAL1 buffer.

5

Ñ

Reserved, should be cleared.

6

CM

Continuous mode

0 Normal operation.

1 The empty bit (RxBD[E]) is not cleared by the CP after this BD is closed, allowing the

associated buffer to be overwritten automatically when the CP next accesses this BD.

7Р15

С

Reserved, should be cleared.

0x02

Ñ

DL

Data length. The number of octets the CP writes into the buffer once its BD is closed.

0x04

Ñ

RXDBPTR Rx data buffer pointer. Points to the Þrst location of the associated buffer; may reside in

either internal or external memory. This pointer must be burst-aligned.

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

Offset + 0x00

E

Ñ

W

I

Ñ

CM

Ñ

CRE

OAM

Ñ

Offset + 0x02

Data Length (DL)/Channel Code (CC)

Offset + 0x04

Rx Data Buffer Pointer (RXDBPTR)

Offset + 0x06

Figure 29-48. AAL0 RxBD