Motorola MPC8260 User Manual

Page 298

10-22

MPC8260 PowerQUICC II UserÕs Manual

MOTOROLA

Part III. The Hardware Interface

8Ð10

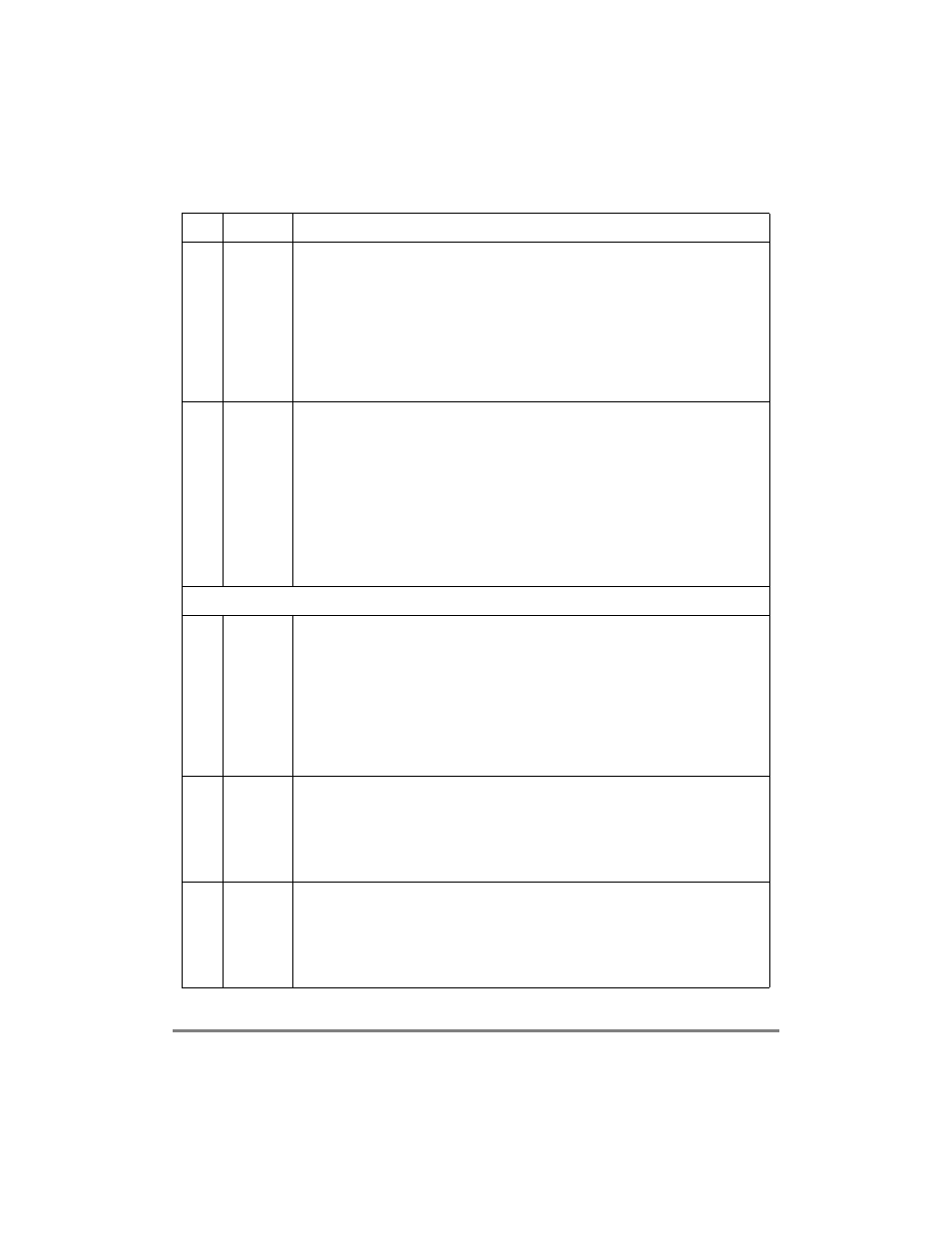

BSMA

Bank select multiplexed address line. Selects the address pins to serve as bank-select address

for the 60x SDRAM. The bank select address can also be output on the BANKSEL pins

(optional). See Section 10.4.5.1, ÒSDRAM Address Multiplexing (SDAM and BSMA).Ó

000 A12ÐA14

001 A13ÐA15

010 A14ÐA16

011 A15ÐA17

100 A16ÐA18

101 A17ÐA19

110 A18ÐA20

111 A19РA21

11Р13

SDA10

ТA10У control. With ORx[PBI], determines which address line can be output to SDA10 during an

ACTIVATE

command, when SDRAM is selected, to control the memory access. See

Section 10.4.12.1, ÒSDRAM ConÞguration Example (Page-Based Interleaving).Ó

For PBI = 0:

000 A12

001 A11

010 A10

011 A9

100 A8

101 A7

110 A6

111 A5

For PBI = 1:

000 A10

001 A9

010 A8

011 A7

100 A6

101 A5

110 A4

111 A3

SDRAM DeviceÐSpeciÞc Parameters:

14Ð16

RFRC

Refresh recovery. DeÞnes the earliest timing for an activate command after a

REFRESH

command. Sets the refresh recovery interval in clock cycles. See Section 10.4.6.6, ÒRefresh

Recovery Interval (RFRC),Ó for how to set this Þeld.

000 Reserved

001 3 clocks

010 4 clocks

011 5 clocks

100 6 clocks

101 7 clocks

110 8 clocks

111 16 clocks

17Ð19 PRETOACT Precharge to activate interval. DeÞnes the earliest timing for

ACTIVATE

or

REFRESH

command

after a precharge command. See Section 10.4.6.1, ÒPrecharge-to-Activate Interval.Ó

001 1 clock-cycle wait states

010 2 clock-cycle wait states

...

111 7 clock-cycle wait states

000 8 clock-cycle wait states

20Ð22

ACTTORW

Activate to read/write interval. DeÞnes the earliest timing for

READ

/

WRITE

command after an

ACTIVATE

command. See Section 10.4.6.2, ÒActivate to Read/Write Interval.Ó

001 1 clock cycle

010 2 clock cycles

...

111 7 clock cycles

000 8 clock cycles

Table 10-7. PSDMR Field Descriptions (Continued)

Bits

Name

Description