Output delay from rts asserted -16 – Motorola MPC8260 User Manual

Page 774

28-16

MPC8260 PowerQUICC II UserÕs Manual

MOTOROLA

Part IV. Communications Processor Module

RTS is asserted when FCC has data to transmit in the transmit FIFO and a falling transmit

clock occurs. At this point, the FCC begins sending the data, once the appropriate

conditions occur on CTS. In all cases, the Þrst bit of data is the start of the opening ßag, or

sync pattern.

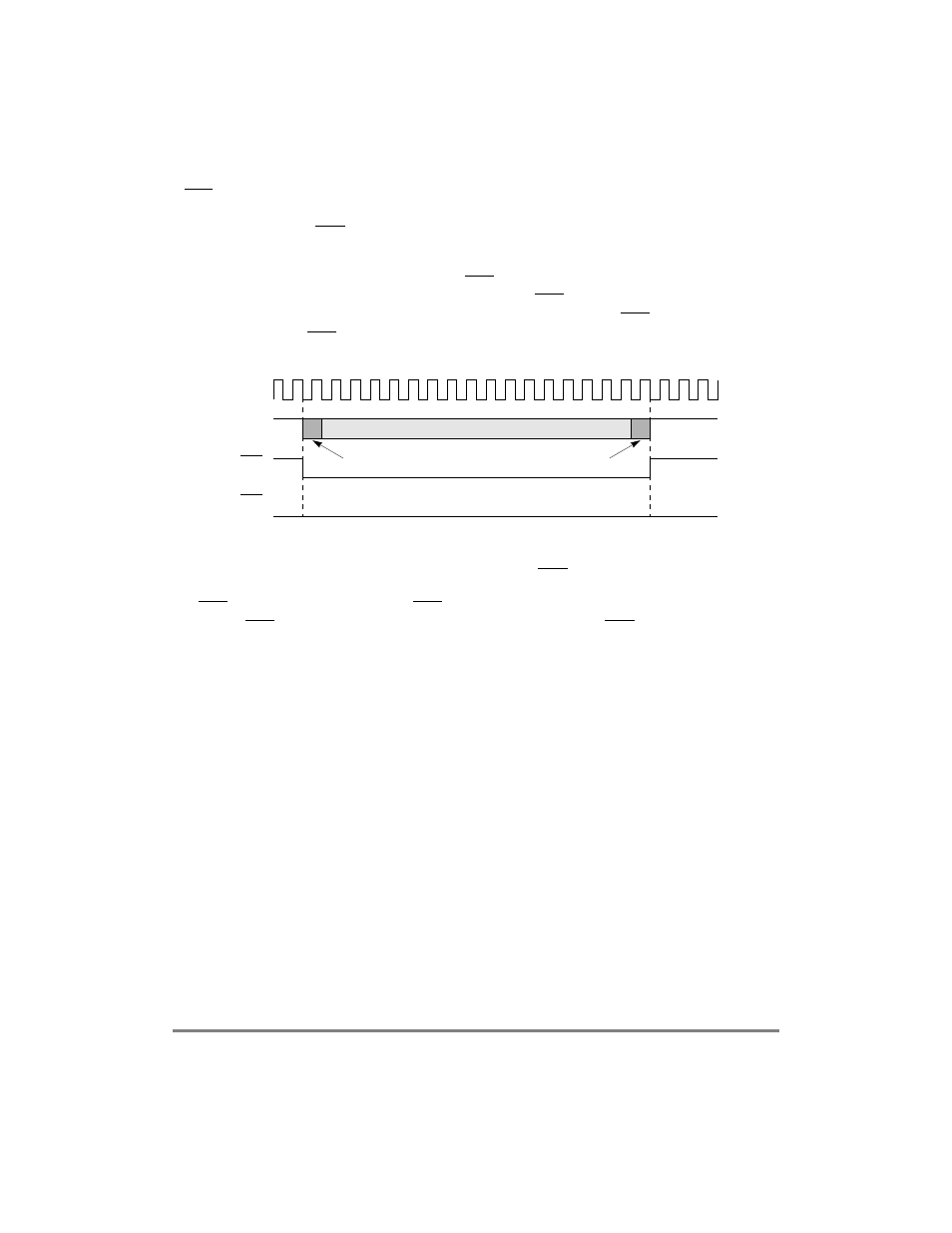

Figure 28-6 shows that the delay between RTS and data is 0 bit times, regardless of the

setting of GFMR[CTSS]. This operation assumes that CTS is either already asserted to the

FCC or is reprogrammed to be a parallel I/O line, in which case the CTS signal to the FCC

is always asserted. RTS is negated one clock after the last bit in the frame.

Figure 28-6. Output Delay from RTS Asserted

If CTS is not already asserted when RTS is asserted, the delays to the Þrst bit of data depend

on when CTS is asserted. Figure shows that the delay between CTS and the data can be

approximately 0.5- to 1-bit time in asynchronous mode (if GFMR[CTSS] = 0) or 0 bit times

(if GFMR[CTSS] = 1).

1. A frame includes opening and closing flags and syncs, if present in the protocol.

TCLK

TXD

Last Bit of Frame Data

First Bit of Frame Data

Note:

(Output)

RTS

(Output)

CTS

(Input)