Hdlc-specific scc parameter ram memory map -4 – Motorola MPC8260 User Manual

Page 612

21-4

MPC8260 PowerQUICC II UserÕs Manual

MOTOROLA

Part IV. Communications Processor Module

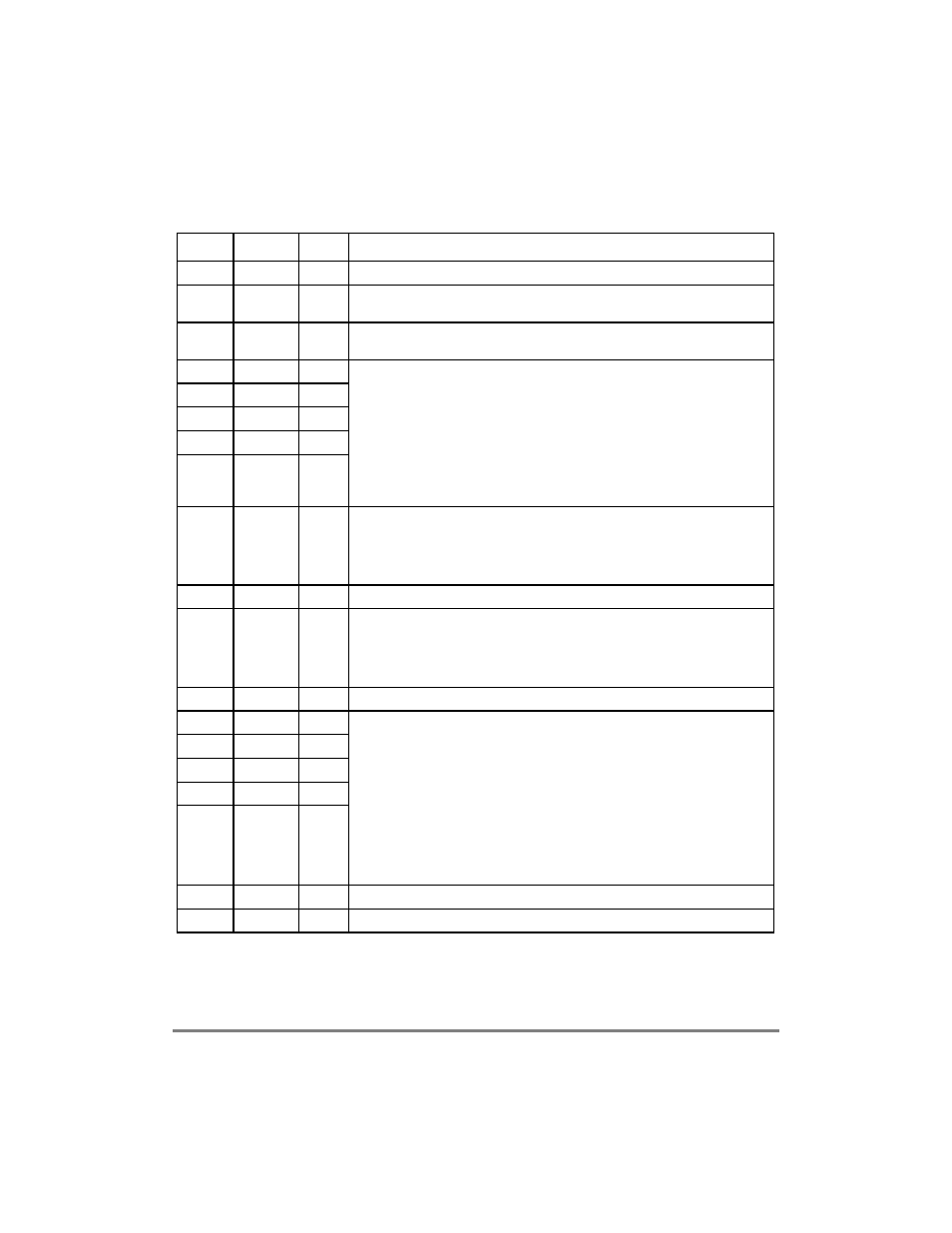

Table 21-1. HDLC-Specific SCC Parameter RAM Memory Map

Offset

1

1

From SCC base. See Section 19.3.1, ÒSCC Base Addresses.Ó

Name

Width

Description

0x30

Ñ

Word

Reserved

0x34

C_MASK

Word

CRC mask. For the 16-bit CRC-CCITT, initialize with 0x0000_F0B8. For 32-bit CRC-

CCITT, initialize with 0xDEBB_20E3.

0x38

C_PRES

Word

CRC preset. For the 16-bit CRC-CCITT, initialize with 0x0000_FFFF. For 32-bit CRC-

CCITT, initialize with 0xFFFF_FFFF.

0x3C

DISFC

Hword

Modulo 2

16

counters maintained by the CP. Initialize them while the channel is

disabled.

DISFC (Discarded frame counter) Counts error-free frames discarded due to lack of

free buffers.

CRCEC (CRC error counter) Includes frames not addressed to the user or frames

received in the BSY condition, but does not include overrun errors.

ABTSC (Abort sequence counter)

NMARC (Nonmatching address received counter) Includes error-free frames only.

RETRC (Frame retransmission counter) Counts number of frames resent due to

collision.

0x3E

CRCEC

Hword

0x40

ABTSC

Hword

0x42

NMARC

Hword

0x44

RETRC

Hword

0x46

MFLR

Hword

Max frame length register. The HDLC compares the incoming HDLC frameÕs length

with the user-deÞned limit in MFLR. If the limit is exceeded, the rest of the frame is

discarded and RxBD[LG] is set in the last BD of that frame. At the end of the frame

the SCC reports frame status and frame length in the last RxBD. The MFLR is

deÞned as all in-frame bytes between the opening and closing ßags.

0x48

MAX_CNT

Hword

Maximum length counter. A temporary down-counter used to track frame length.

0x4A

RFTHR

Hword

Received frames threshold. Used to reduce potential interrupt overhead when each

in a series of short HDLC frames causes an SCCE[RXF] event. Setting RFTHR

determines the frequency of RXF interrupts, which occur only when the RFTHR limit

is reached. Provide enough empty RxBDs for the number of frames speciÞed in

RFTHR.

0x4C

RFCNT

Hword

Received frames count. RFCNT is a down-counter used to implement RFTHR.

0x4E

HMASK

Hword

Mask register (HMASK) and four address registers (HADDRn) for address

recognition. The SCC reads the frame address from the HDLC receiver, compares it

with the HADDRs, and masks the result with HMASK. Setting an HMASK bit enables

the corresponding comparison bit, clearing a bit masks it. When a match occurs, the

frame address and data are written to the buffers. When no match occurs and a

frame is error-free, the nonmatching address received counter (NMARC) is

incremented.

The eight low-order bits of HADDRn should contain the Þrst address byte after the

opening ßag. For example, to recognize a frame that begins 0x7E (ßag), 0x68, 0xAA,

using 16-bit address recognition, HADDRn should contain 0xAA68 and HMASK

should contain 0xFFFF. For 8-bit addresses, clear the eight high-order HMASK bits.

See Figure 21-2.

0x50

HADDR1

Hword

0x52

HADDR2

Hword

0x54

HADDR3

Hword

0x56

HADDR4

Hword

0x58

TMP

Hword

Temporary storage.

0x5A

TMP_MB

Hword

Temporary storage.