6 sdram device-specific parameters, 1 precharge-to-activate interval, Sdram device-specific parameters -38 – Motorola MPC8260 User Manual

Page 314: Precharge-to-activate interval -38, Sdram address multiplexing (a16ða31) -38, 6 sdram device-speciþc parameters

10-38

MPC8260 PowerQUICC II UserÕs Manual

MOTOROLA

Part III. The Hardware Interface

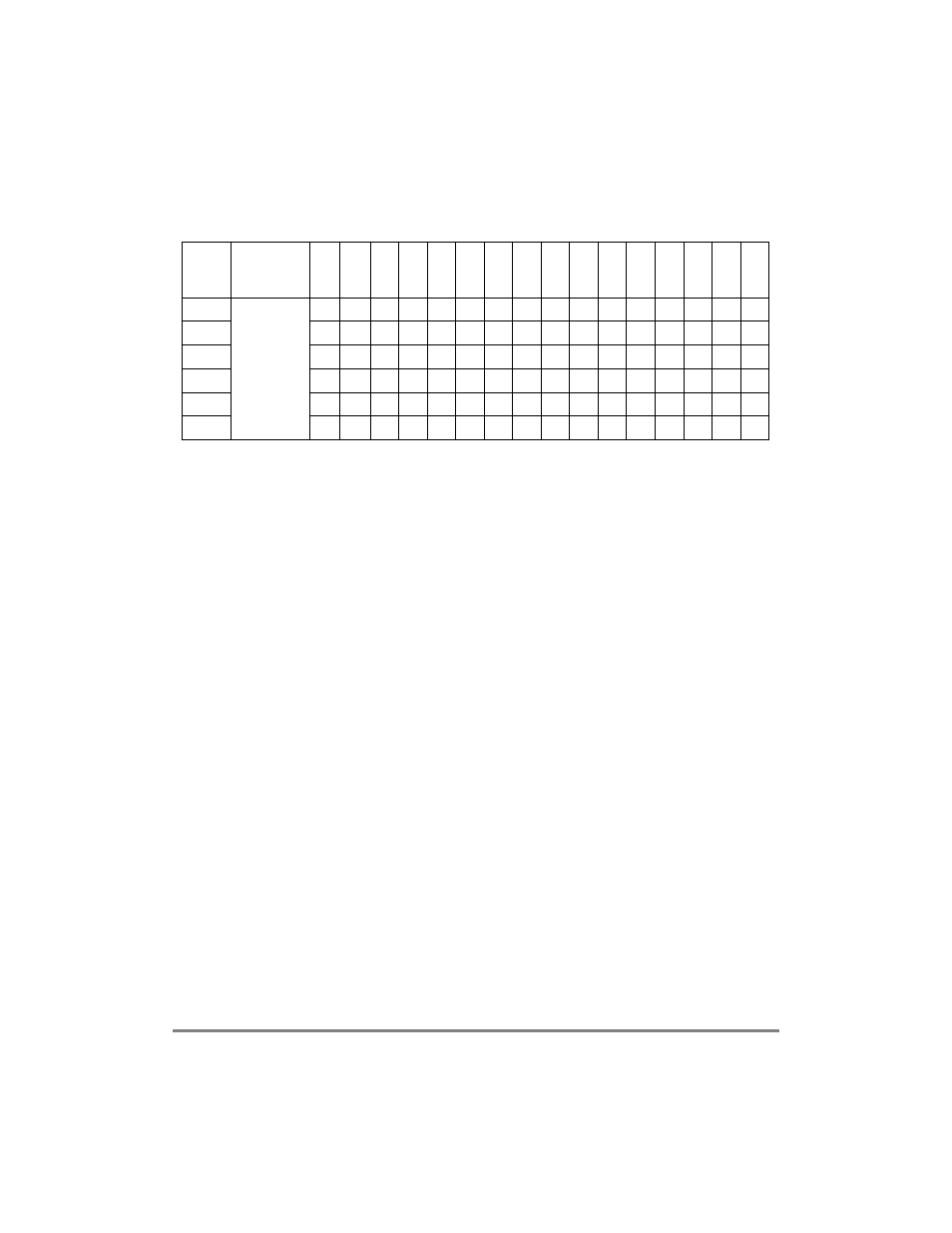

Table 10-20 shows SDRAM address multiplexing for A16ÐA31.

10.4.6 SDRAM Device-SpeciÞc Parameters

The software is responsible for setting correct values to some device-speciÞc parameter that

can be extracted from the data sheet. The values are stored in the ORx and P/LSDMR

registers. These parameters include the following:

¥

Precharge to activate interval (P/LSDMR[PRETOACT]). See Section 10.4.6.1,

ÒPrecharge-to-Activate Interval.Ó

¥

Activate to read/write interval (P/LSDMR[ACTTORW]). See Section 10.4.6.2,

ÒActivate to Read/Write Interval.Ó

¥

CAS latency, column address to Þrst data out (P/LSDMR[CL]). See

Section 10.4.6.3, ÒColumn Address to First Data OutÑCAS Latency.Ó

¥

Last data out to precharge (P/LSDMR[LDOTOPRE]). Section 10.4.6.4, ÒLast Data

Out to Precharge.Ó

¥

Write recovery, last data in to precharge (P/LSDMR[WRC]). See Section 10.4.6.5,

ÒLast Data In to PrechargeÑWrite Recovery.Ó

¥

Refresh recovery interval (P/LSDMR[RFRC]). See Section 10.4.6.6, ÒRefresh

Recovery Interval (RFRC).Ó

¥

External address multiplexing present (P/LSDMR[EAMUX]). See Section 10.4.6.7,

ÒExternal Address Multiplexing Signal.Ó

¥

External buffers on the control lines present (P/LSDMR[BUFCMD]). See

Section 10.4.6.8, ÒExternal Address and Command Buffers (BUFCMD).Ó

The following sections describe the SDRAM parameters that are programmed in the P/

LSDMR register.

10.4.6.1 Precharge-to-Activate Interval

This parameter, controlled by P/LSDMR[PRETOACT] deÞnes the earliest timing for

activate or refresh command after a precharge command.

Table 10-20. SDRAM Address Multiplexing (A16ÐA31)

SDAM

External Bus

Address

Pins

A16 A17 A18 A19 A20 A21 A22 A23 A24 A25 A26 A27 A28 A29 A30 A31

000

Signal driven

on external

pins when

address

multiplexing

is enabled

A8

A9

A10 A11 A12 A13 A14 A15 A16 A17 A18 A19 A20 A21 A22 A23

001

A7

A8

A9

A10 A11 A12 A13 A14 A15 A16 A17 A18 A19 A20 A21 A22

010

A6

A7

A8

A9

A10 A11 A12 A13 A14 A15 A16 A17 A18 A19 A20 A21

011

A5

A6

A7

A8

A9

A10 A11 A12 A13 A14 A15 A16 A17 A18 A19 A20

100

Ñ

A5

A6

A7

A8

A9

A10 A11 A12 A13 A14 A15 A16 A17 A18 A19

101

С

С

A5

A6

A7

A8

A9

A10 A11 A12 A13 A14 A15 A16 A17 A18