6 risc timer tables, Risc timer tables -18, Parameter ram -18 – Motorola MPC8260 User Manual

Page 448: See rand in table 13-10, Wn in table 13-10

13-18

MPC8260 PowerQUICC II UserÕs Manual

MOTOROLA

Part IV. Communications Processor Module

13.6 RISC Timer Tables

The CP can control up to 16 software timers that are separate from the four general-purpose

timers and the BRGs in the CPM. These timers are best used in protocols that do not require

extreme precision, but in which it is preferable to free the core from scanning the softwareÕs

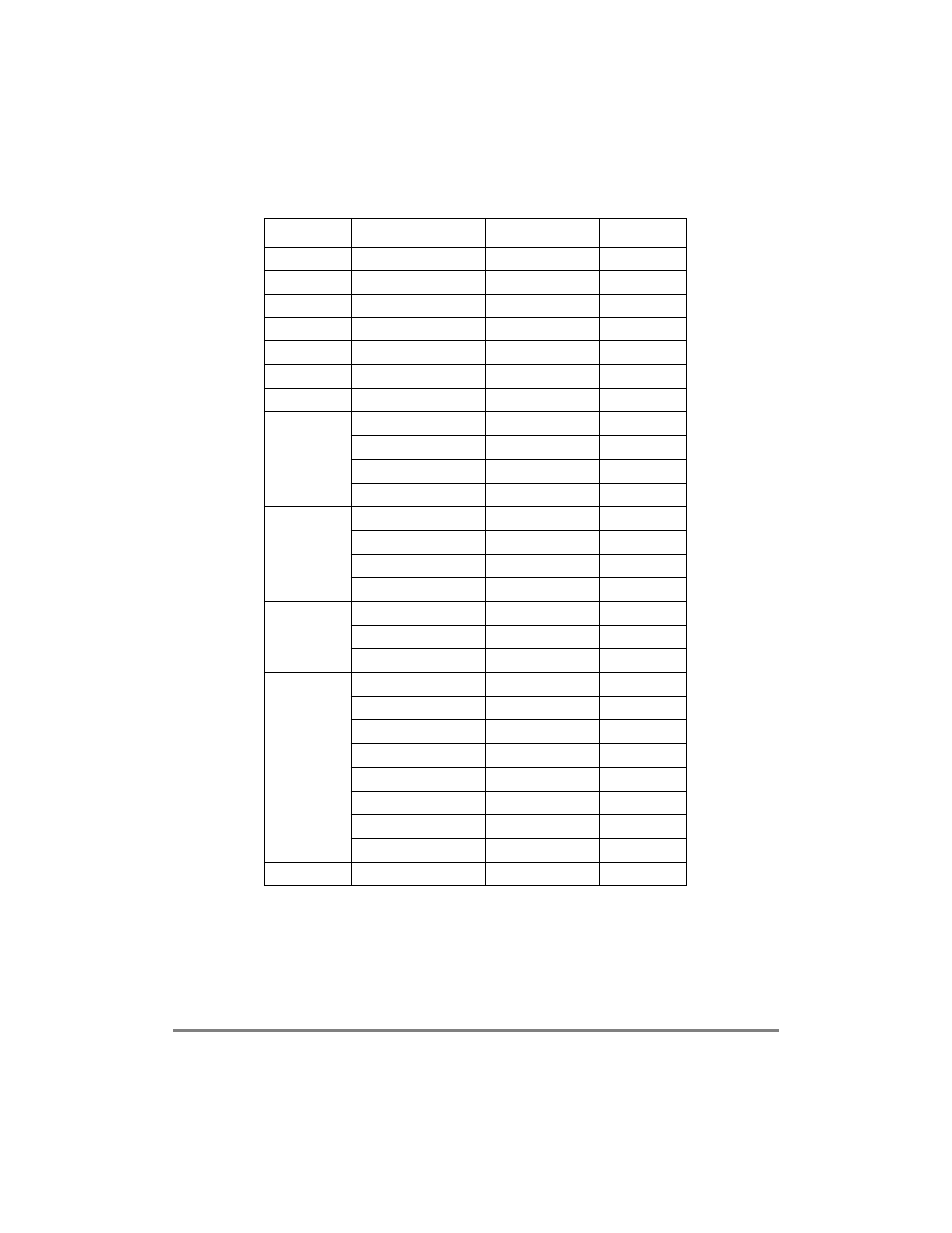

Table 13-10. Parameter RAM

Page

Address

1

1

Offset from RAM_BASE

Peripheral

Size (Bytes)

1

0x8000 SCC1

256

2

0x8100

SCC2 256

3

0x8200

SCC3

256

4

0x8300

SCC4

256

5 0x8400

FCC1

256

6

0x8500

FCC2

256

7

0x8600

FCC3

256

8

0x8700

MCC1

128

0x8780

Reserved

124

0x87FC

SMC1_BASE

2

0x87FE

IDMA1_BASE

2

9

0x8800

MCC2

128

0x8880

Reserved

124

0x88FC

SMC2_BASE

2

0x88FE

IDMA2_BASE

2

10

0x8900

Reserved

252

0x89FC

SPI_BASE

2

0x89FE

IDMA3_BASE

2

11

0x8A00

Reserved

224

0x8AE0

RISC Timers

16

0x8AF0

REV_NUM

2

0x8AF2

Reserved

2

0x8AF4

Reserved

4

0x8AF8

RAND

4

0x8AFC

I

2

C_BASE

2

0x8AFE

IDMA4_BASE

2

12-16

0x8B00

Reserved

1280