12 idma programming examples, Idma programming examples -29, Parallel i/o register programmingñport d -29 – Motorola MPC8260 User Manual

Page 553: Example: peripheral-to-memory modeñidma2 -29, Able 18-14 (optional) for, Able 18-14. see section 35.2, òport

MOTOROLA

Chapter 18. SDMA Channels and IDMA Emulation

18-29

Part IV. Communications Processor Module

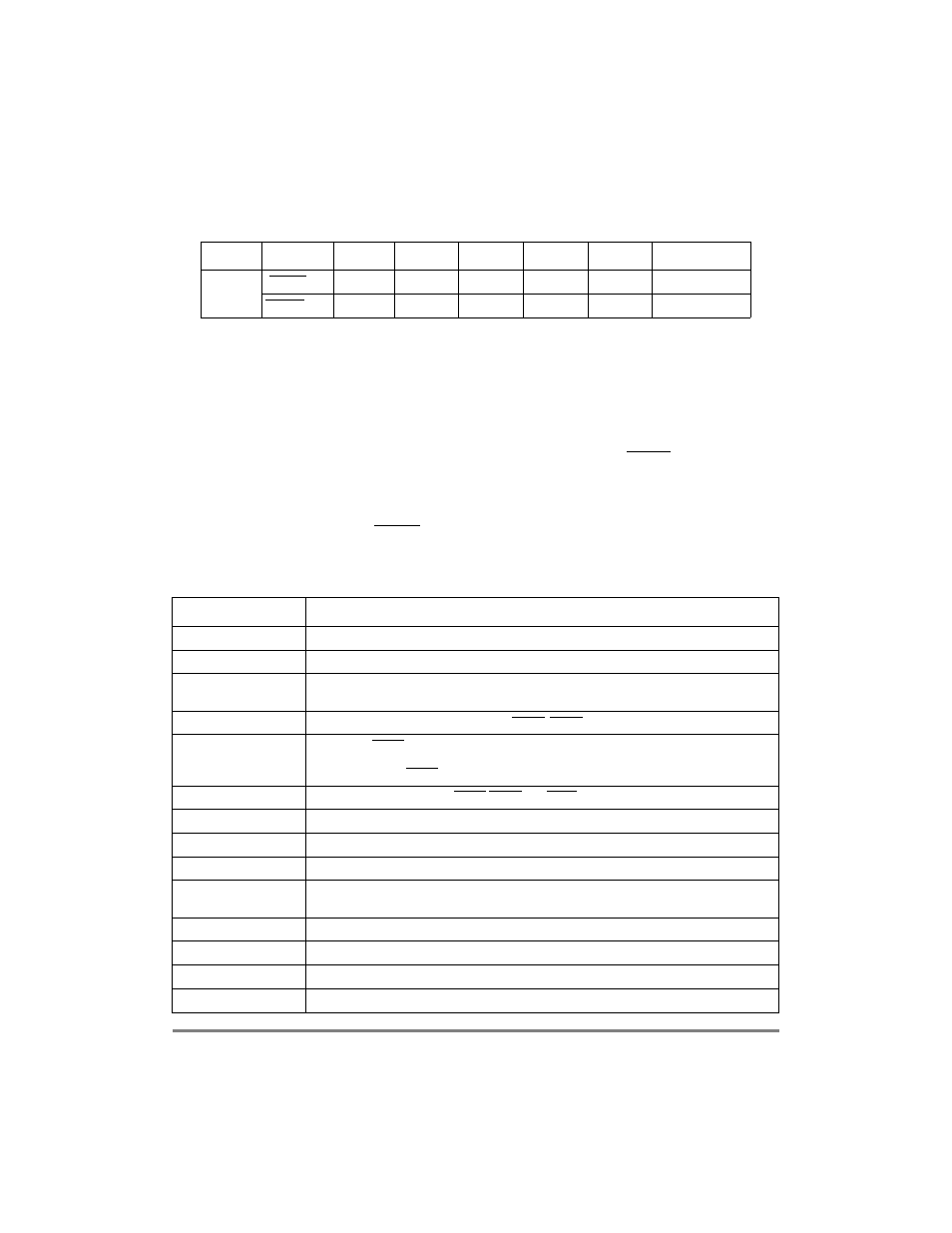

Table 18-14 describes parallel I/O register programming for port D (optional).

18.12 IDMA Programming Examples

These programming examples demonstrate the use of most of the different modes and

conÞgurations of the IDMA channels.

18.12.1 Peripheral-to-Memory Mode (60x Bus to Local Bus)ÑIDMA2

In the example in Table 18-15, the IDMA2 channel reads 8 bytes per DREQ assertion from

a Þxed address peripheral located on the 60x bus into the internal buffer. When there is

enough data in the internal buffer, it writes one burst to the memory located on the local

bus. The internal buffer size is set to 64 bytes to handle maximum transfer of a single burst.

The IDMA2 channel asserts DONE on the last read transfer of the last BD to notify the

peripheral that there is no data left to transfer.

Table 18-14. Parallel I/O Register ProgrammingÑPort D

Channel

Signal

Pin

PPARD

PDIRD

PODRD

PSORD

Default

IDMA1

DACK1 (O)

PD[6]

1

1

0

1

Ñ

DONE1 (I/O)

PD[5]

1

0

1

1

VDD

Table 18-15. Example: Peripheral-to-Memory ModeÑIDMA2

Important Init Values

Description

DCM(FB) = 0

Not in ßy-by mode.

DCM(LP) = 0

Transfers to memory have middle CPM request priority. The destination bus is not overloaded.

DCM(DMA_WRAP) =

000

The internal buffer is 64 bytes long to support 32-byte transfers to memory on the destination

bus (one 60x burst) on steady-state of work.

DCM(ERM) = 1

Transfers from peripheral are initiated by DREQ. DONE assertion is supported.

DCM(DT) = 0

Assertion of DONE by the peripheral causes the transfer to be terminated, after writing all the

data in the internal buffer to memory, interrupt EDN is set to the core, IDMA channel is

stopped. additional DREQ assertions are ignored, until

START

_

IDMA

command is issued.

DCM(S/D) = 10

Peripheral-to-memory mode. DONE DREQ and DACK are connected to the peripheral.

DCM(SINC) = 0

The peripheral address are not incremented after transfers, Þxed location.

DCM(DINC) = 1

The memory address is incremented after every transfer.

DPR_BUF = 0x0DC0

Initiated to address aligned to 64 (bit[5Ð0]= 00000).

IBASE = IBDPTR =

0x0030

The current BD pointer is set to the BD table base address (aligned 16 -bits[3Ð0] = 0).

STS = 8 (0x0008)

Transfers from peripheral are always single 8-byte accesses.

DTS = 32 (0x0020)

Transfers to memory are 32 bytes long (60x bursts) on steady-state of work.

Every BD(SDTB) = 1

Peripheral is on the 60x bus.

Every BD(DDTB) = 0

Memory is on the local bus.