Motorola MPC8260 User Manual

Page 129

MOTOROLA

Chapter 3. Memory Map

3-9

Part I. Overview

I

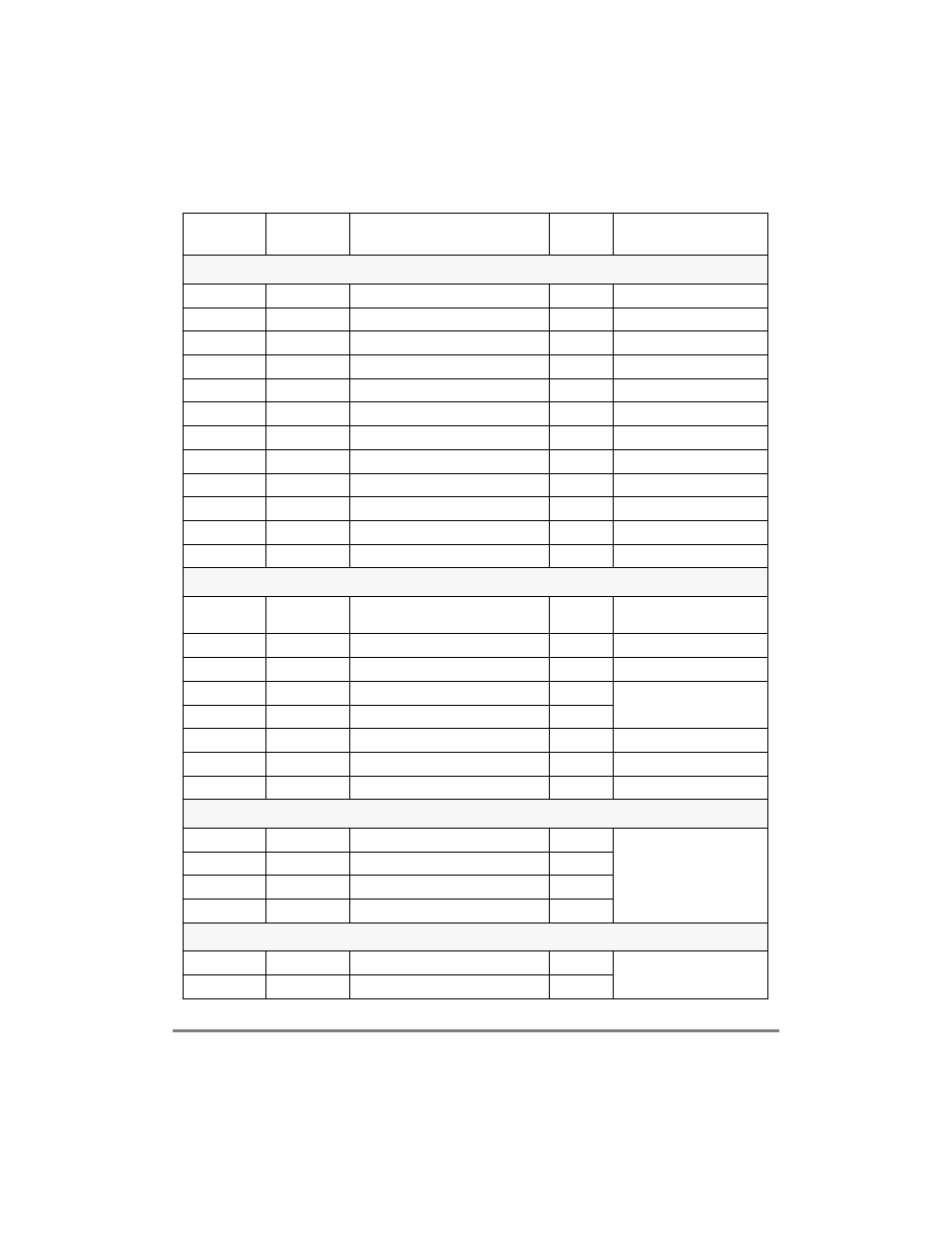

2

C

11860

I2MOD

I

2

C mode register

8 bits

11862

Reserved

Ñ

24 bits

Ñ

11864

I2ADD

I

2

C address register

8 bits

11866

Reserved

Ñ

24 bits

Ñ

11868

I2BRG

I

2

C BRG register

8 bits

1186A

Reserved

Ñ

24 bits

Ñ

1186C

I2COM

I

2

C command register

8 bits

1186E

Reserved

Ñ

24 bits

Ñ

11870

I2CER

I

2

C event register

8 bits

11872

Reserved

Ñ

24 bits

Ñ

11874

I2CMR

I

2

C mask register

8 bits

11875Ð119BF

Reserved

Ñ

315 bytes

Ñ

Communications Processor

119C0

CPCR

Communications processor command

register

32 bits

119C4

RCCR

CP conÞguration register

32 bits

119C8Ð119D5

Reserved

Ñ

12 bytes

Ñ

119D6

RTER

CP timers event register

16 bits

119DA

RTMR

CP timers mask register

16 bits

119DC

RTSCR

CP time-stamp timer control register

16 bits

119DE

Reserved

Ñ

16 bits

119E0

RTSR

CP time-stamp register

32 bits

BRGs 1Ð4

119F0

BRGC1

BRG1 conÞguration register

32 bits

119F4

BRGC2

BRG2 conÞguration register

32 bits

119F8

BRGC3

BRG3 conÞguration register

32 bits

119FC

BRGC4

BRG4 conÞguration register

32 bits

SCC1

11A00

GSMR_L1

SCC1 general mode register

32 bits

11A04

GSMR_H1

SCC1 general mode register

32 bits

Table 3-1. Internal Memory Map (Continued)

Internal

Address

Abbreviation

Name

Size

Section/Page Number