6 siu interrupt vector register (sivec), Siu interrupt vector register (sivec) -23, Simr_l register -23 – Motorola MPC8260 User Manual

Page 161

4-23

MPC8260 PowerQUICC II UserÕs Manual

MOTOROLA

Part II. ConÞguration and Reset

Note the following:

¥

SCC/MCC/FCC SIMR bit positions are not affected by their relative priority.

¥

The user can clear pending register bits that were set by multiple interrupt events

only by clearing all unmasked events in the corresponding event register.

¥

If an SIMR bit is masked at the same time that the corresponding SIPNR bit causes

an interrupt request to the core, the error vector is issued (if no other interrupts

pending). Thus, the user should always include an error vector routine, even if it

contains only an rÞ instruction. The error vector cannot be masked.

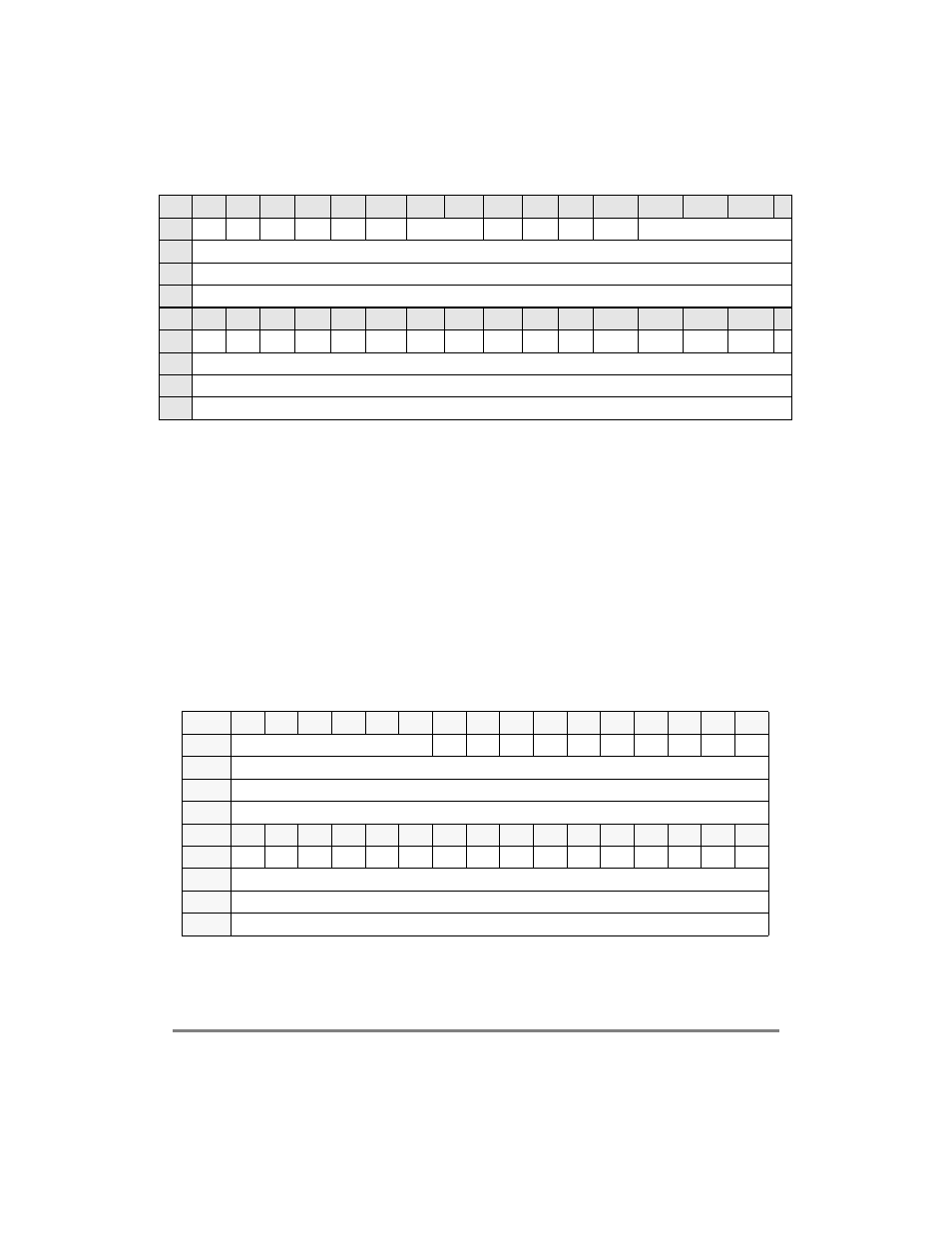

4.3.1.6 SIU Interrupt Vector Register (SIVEC)

The SIU interrupt vector register (SIVEC), shown in Figure 4-18, contains an 8-bit code

representing the unmasked interrupt source of the highest priority level.

Bits

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

Field FCC1 FCC2 FCC3

Ñ

MCC1 MCC2

Ñ

SCC1 SCC2 SCC3 SCC4

Ñ

Reset

0000_0000_0000_0000

R/W

R/W

Addr

Bits

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

Field

I2C

SPI

RTT SMC1 SMC2 IDMA1 IDMA2 IDMA3 IDMA4 SDMA

Ñ

TIMER1 TIMER2 TIMER3 TIMER4 Ñ

Reset

0000_0000_0000_0000

R/W

R/W

Addr

0x10C22

Figure 4-17. SIMR_L Register

Bit

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

Field

Interrupt Code

0

0

0

0

0

0

0

0

0

0

Reset

0000_0000_0000_0000

R/W

R

Addr

Bit

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

Field

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Reset

0000_0000_0000_0000

R/W

R

Addr

0x10C06

Figure 4-18. SIU Interrupt Vector Register (SIVEC)