Motorola MPC8260 User Manual

Page 563

MOTOROLA

Chapter 19. Serial Communications Controllers (SCCs)

19-7

Part IV. Communications Processor Module

7

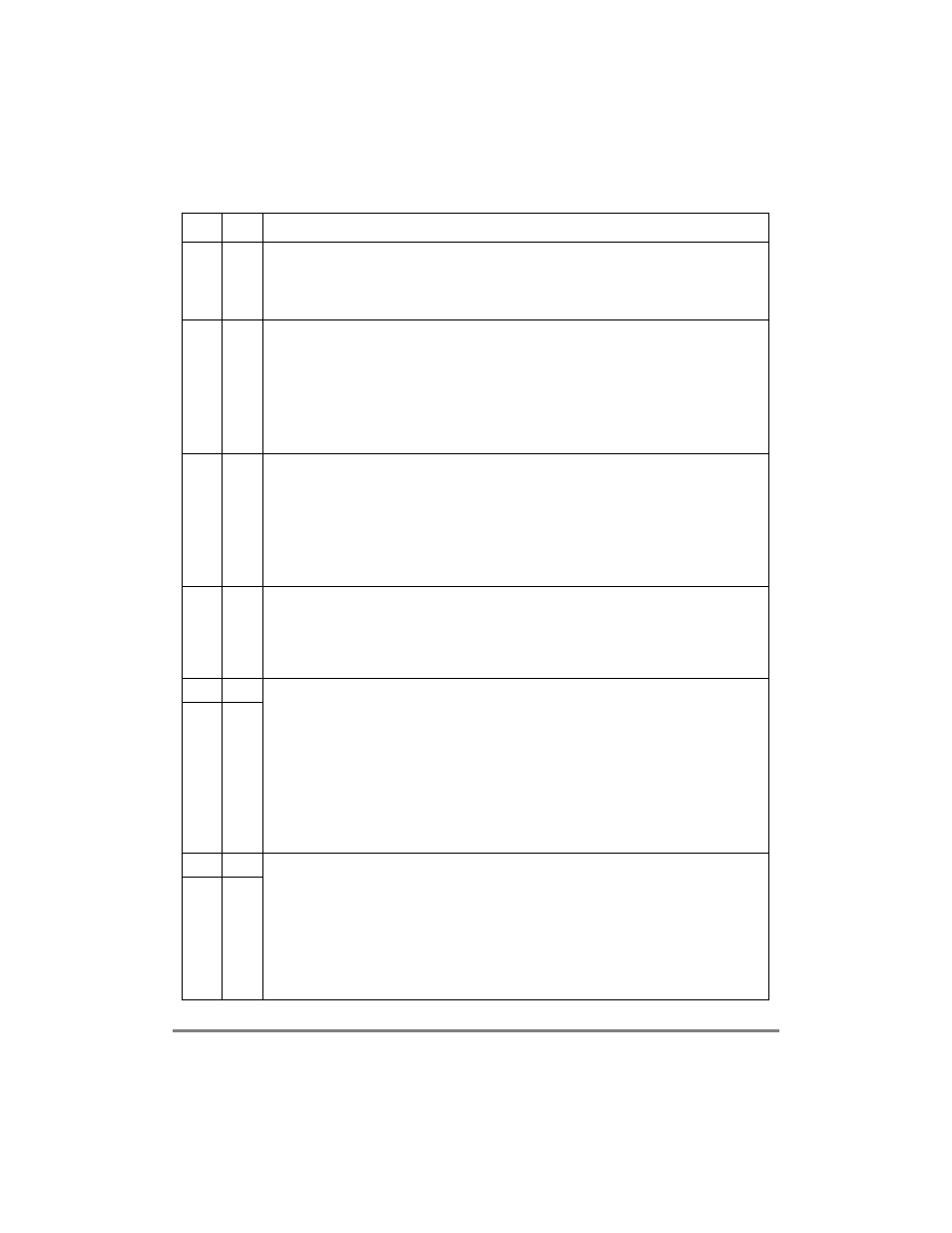

TINV

DPLL Tx input invert data. Must be zero in HDLC bus mode.

0 Do not invert.

1 Invert data before sending it to the DPLL for transmission. Used to produce FM1 from FM0 and

NRZI space from NRZI mark and to invert the data stream in regular NRZ mode. In T1 applications,

setting TINV and TEND creates a continuously inverted HDLC data stream.

8Ð10

TPL

Tx preamble length. Determines the length of the preamble conÞgured by the TPP bits.

000 No preamble (default).

001 8 bits (1 byte).

010 16 bits (2 bytes).

011 32 bits (4 bytes).

100 48 bits (6 bytes). Select this setting for Ethernet operation.

101 64 bits (8 bytes).

110 128 bits (16 bytes).

111 Reserved.

11Ð12 TPP

Tx preamble pattern. Determines what, if any, bit pattern should precede each Tx frame. The

preamble pattern is sent before the Þrst ßag/sync of the frame. TPP is ignored in UART mode. The

preamble length is programmed in TPL; the preamble pattern is typically sent to a receiving station

that uses a DPLL for clock recovery. The receiving DPLL uses the regular preamble pattern to help it

lock onto the received signal in a short, predictable time period.

00 All zeros.

01 Repetitive 10s. Select this setting for Ethernet operation.

10 Repetitive 01s.

11 All ones. Select this setting for LocalTalk operation.

13

TEND

Transmitter frame ending. Intended for NMSI transmitter encoding of the DPLL. TEND determines

whether TXD should idle in a high state or in an encoded ones state (high or low). It can, however, be

used with other encodings besides NMSI.

0 Default operation. TXD is encoded only when data is sent, including the preamble and opening and

closing ßags/syncs. When no data is available to send, the signal is driven high.

1 TXD is always encoded, even when idles are sent.

14Ð15 TDCR Transmitter/receiver DPLL clock rate. If the DPLL is not used, choose 1

´ mode except in

asynchronous UART mode where 8

´, 16´, or 32´ must be chosen. TDCR should match RDCR in

most applications to allow the transmitter and receiver to use the same clock source. If an application

uses the DPLL, the selection of TDCR/RDCR depends on the encoding/decoding. If communication

is synchronous, select 1

´. FM0/FM1, Manchester, and Differential Manchester require 8´, 16´, or

32

´. If NRZ- or NRZI-encoded communication is asynchronous (that is, clock recovery required),

select 8

´, 16´, or 32´. The 8´ option allows highest speed, whereas the 32´ option provides the

greatest resolution.

00 1

´ clock mode. Only NRZ or NRZI encodings/decodings are allowed.

01 8

´ clock mode.

10 16

´ clock mode. Normally chosen for UART and AppleTalk.

11 32

´ clock mode.

16Ð17 RDCR

18Ð20 RENC Receiver decoding/transmitter encoding method. Select NRZ if DPLL is not used. RENC should equal

TENC in most applications. However, do not use this internal DPLL for Ethernet.

000 NRZ (default setting if DPLL is not used). Required for UART (synchronous or asynchronous).

001 NRZI Mark (set RINV/TINV also for NRZI space).

010 FM0 (set RINV/TINV also for FM1).

011 Reserved.

100 Manchester.

101 Reserved.

110 Differential Manchester (Differential Bi-phase-L).

111 Reserved.

21Ð23 TENC

Table 19-2. GSMR_L Field Descriptions (Continued)

Bit

Name

Description