Cpm low interrupt priority register (scprr_l) -20, Scprr_h field descriptions -20, Scprr_l field descriptions -20 – Motorola MPC8260 User Manual

Page 158

4-20

MPC8260 PowerQUICC II UserÕs Manual

MOTOROLA

Part II. ConÞguration and Reset

Table 4-6 describes SCPRR_H Þelds.

The CPM low interrupt priority register (SCPRR_L), shown in Figure 4-13, deÞnes

prioritization of SCCs.

Table 4-7 describes SCPRR_L Þelds.

Table 4-6. SCPRR_H Field Descriptions

Bits

Name

Description

0Ð2

XC1PÐXCC1

Priority order. DeÞnes which FCC/MCC asserts its request in the XCC1 priority position.

The user should not program the same FCC/MCC to more than one priority position (1Ð8).

These bits can be changed dynamically.

000 FCC1 asserts its request in the XCC1 position.

001 FCC2 asserts its request in the XCC1 position.

010 FCC3 asserts its request in the XCC1 position.

011 XCC1 position not active.

100 MCC1 asserts its request in the XCC1 position.

101 MCC2 asserts its request in the XCC1 position.

110 XCC1 position not active.

111 XCC1 position not active.

3Ð12

XC2PÐXC8P

Same as XC1P, but for XCC2ÐXCC8

13Р15

С

Reserved, should be cleared.

Bits

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

Field

YC1P

YC2P

YC3P

YC4P

Ñ

Reset

000

001

010

011

0000

R/W

R/W

Addr

Bits

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

Field

YC5P

YC6P

YC7P

YC8P

Ñ

Reset

100

101

110

111

0000

R/W

R/W

Addr

0x10C20

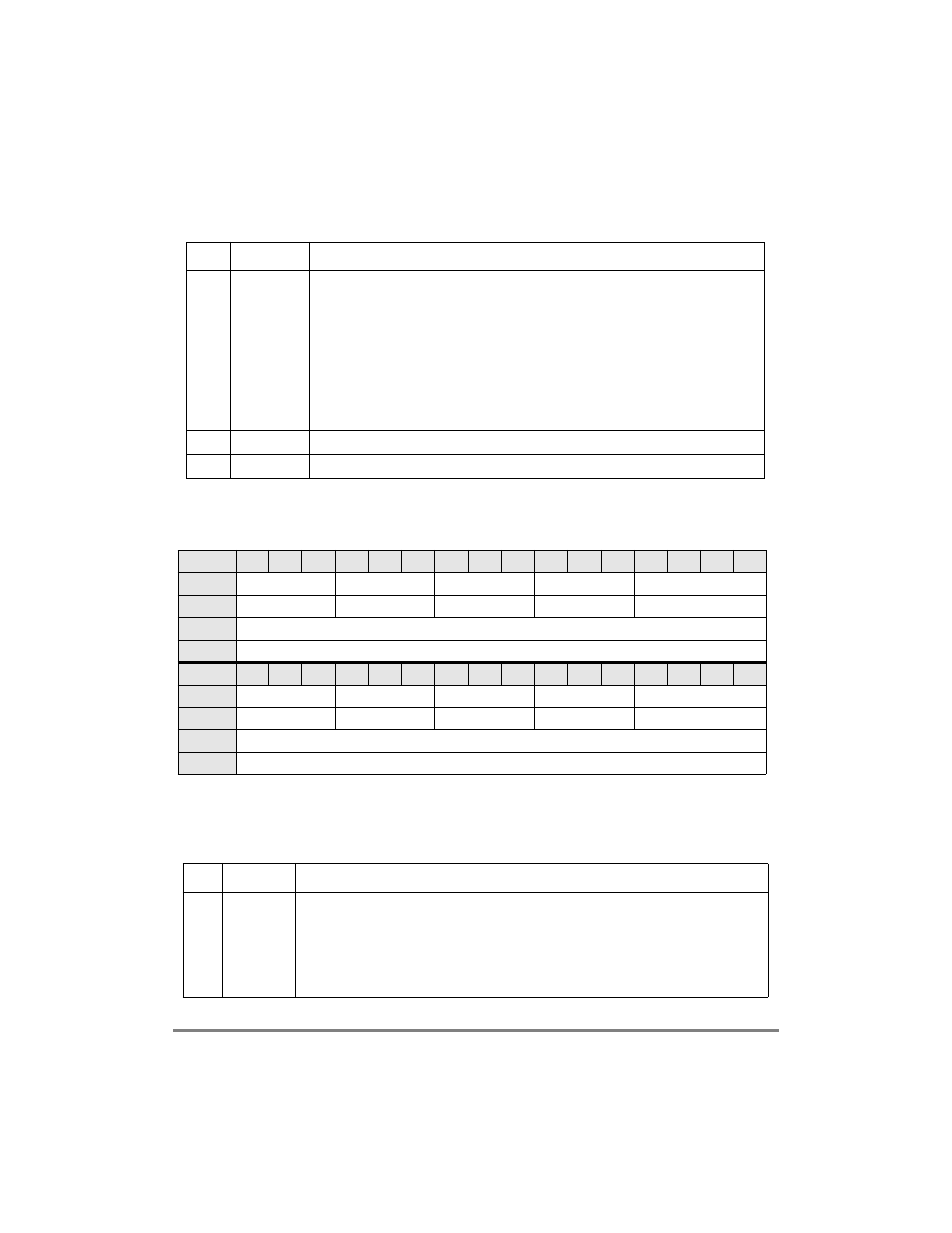

Figure 4-13. CPM Low Interrupt Priority Register (SCPRR_L)

Table 4-7. SCPRR_L Field Descriptions

Bits

Name

Description

0Ð2

YC1PÐYCC1 Priority order. DeÞnes which SCC asserts its request in the YCC1 priority position. Do not

program the same SCC to multiple priority positions. This Þeld can be changed dynamically.

000 SCC1 asserts its request in the YCC1 position.

001 SCC2 asserts its request in the YCC1 position.

010 SCC3 asserts its request in the YCC1 position.

011 SCC4 asserts its request in the YCC1 position.

1XX YCC1 position is not active.