Clock ratios -68 – Motorola MPC8260 User Manual

Page 344

10-68

MPC8260 PowerQUICC II UserÕs Manual

MOTOROLA

Part III. The Hardware Interface

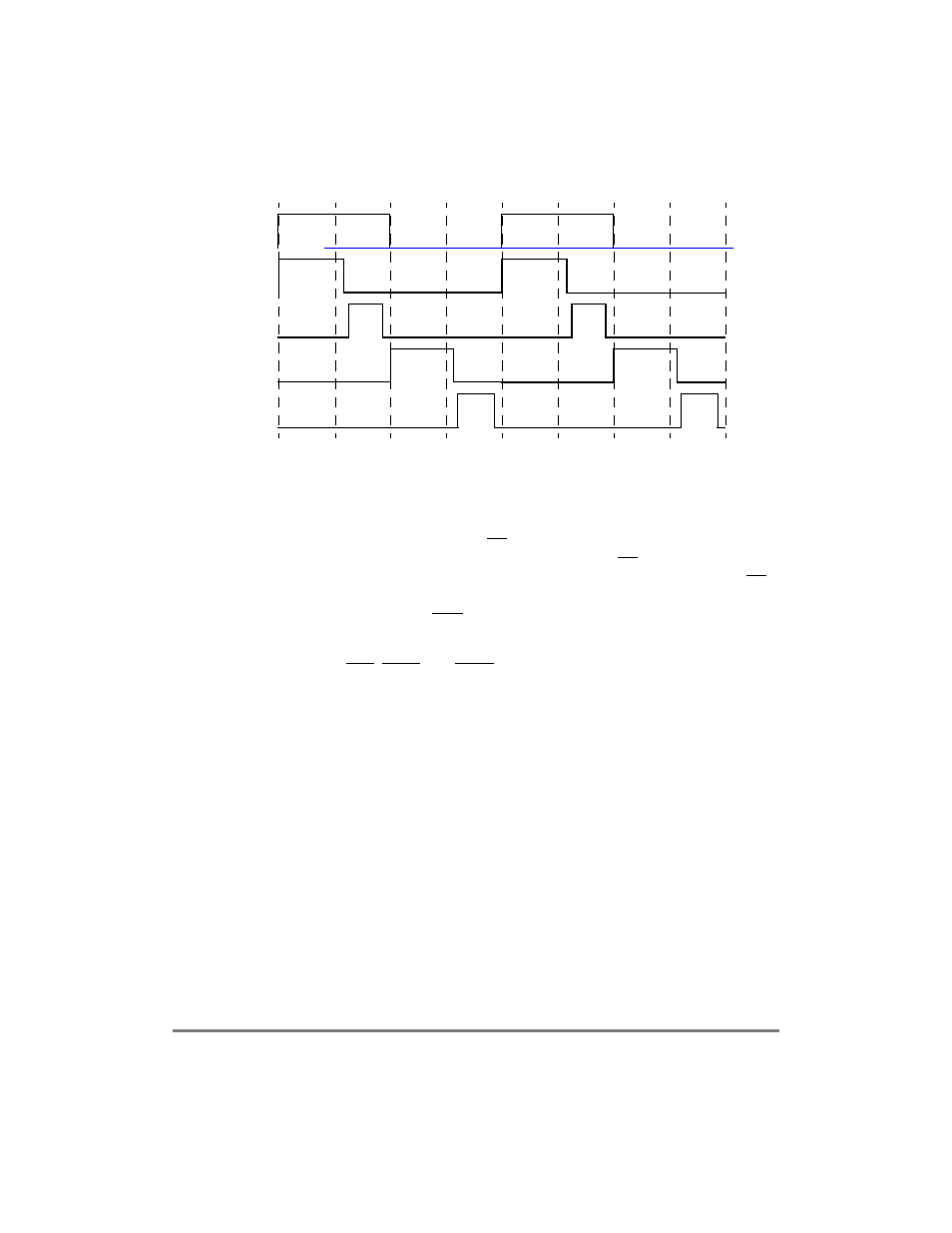

Figure 10-59. Memory Controller UPM Clock Scheme for Non-Integer (2.5:1/3.5:1)

Clock Ratios

The state of the external signals may change (if speciÞed in the RAM array) at any positive

edge of T1, T2, T3, or T4 (there is a propagation delay speciÞed in the MPC8260 Hardware

SpeciÞcations). Note however that only the CS signal corresponding to the currently

accessed bank is manipulated by the UPM pattern when it runs. The BS signal assertion and

negation timing is also speciÞed for each cycle in the RAM word; which of the four BS

signals are manipulated depends on the port size of the speciÞed bank, the external address

accessed, and the value of TSIZn. The GPL lines toggle as programmed for any access that

initiates a particular pattern, but resolution of control is limited to T1 and T3.

Figure 10-60 shows how CSx, GPL1, and GPL2 can be controlled. A word is read from the

RAM that speciÞes on every clock cycle the logical bits CST1, CST2, CST3, CST4, G1T1,

G1T3, G2T1, and G2T3. These bits indicate the electrical value for the corresponding

output pins at the appropriate timing.

CLKIN

T1

T2

T3

T4