Machine x mode registers (mxmr) -27, Table 10-9 describes m x mr bits – Motorola MPC8260 User Manual

Page 303

MOTOROLA

Chapter 10. Memory Controller

10-27

Part III. The Hardware Interface

Table 10-9 describes MxMR bits.

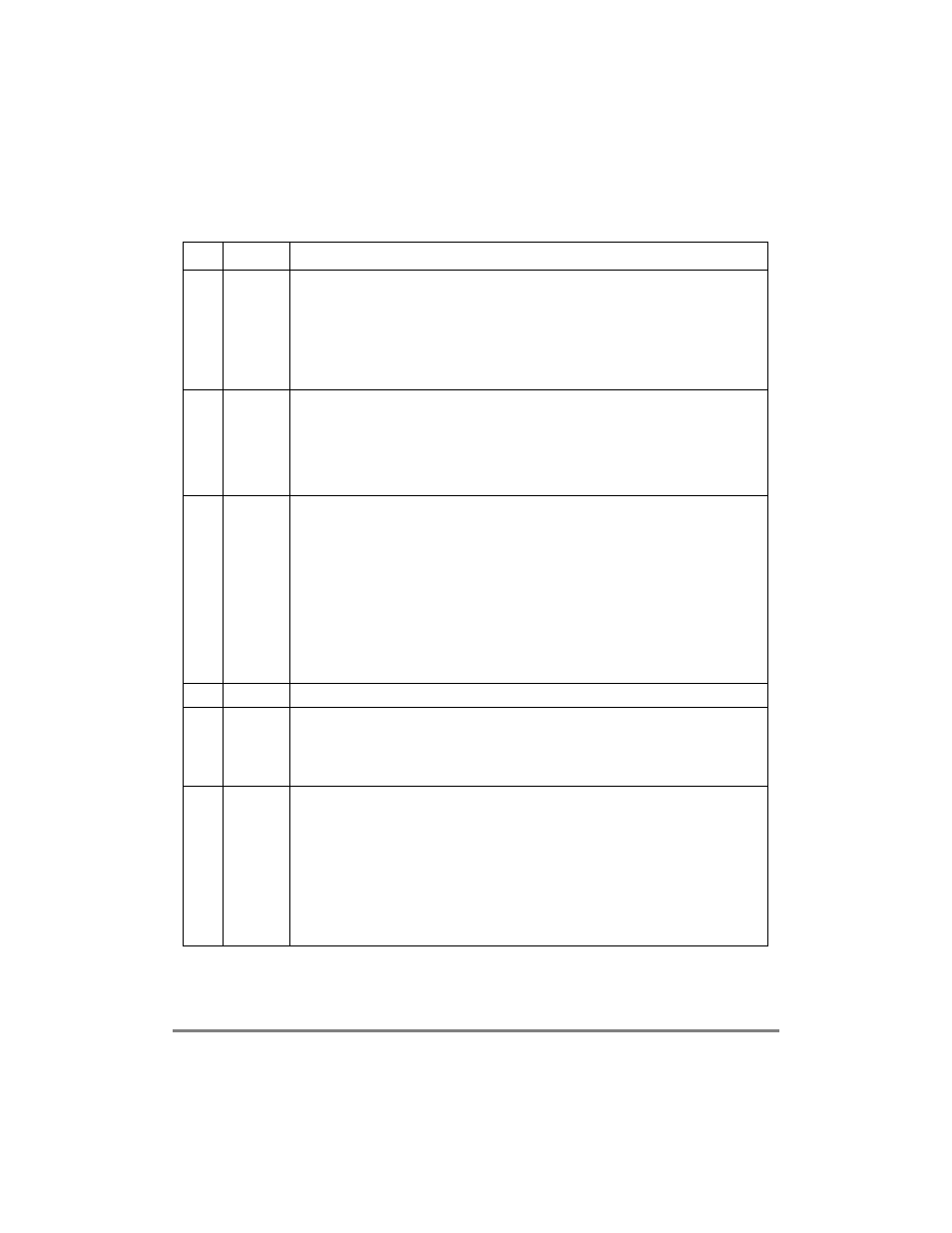

Table 10-9. Machine x Mode Registers (MxMR)

Bits

Name

Description

0

BSEL

Bus select. Assigns banks that select UPMx to the 60x or local bus.

0 Banks that select UPMx are assigned to the 60x bus.

1 Banks that select UPMx are assigned to the local bus.

Note: if refresh is required, the UPMÕs should be assigned as follows:

UPMA: 60x bus (if 60x bus refresh needed)

UPMB: Local bus (if local bus refresh required)

UPMC: any bus, as long as UPMA or UPMB is used on the relevant bus.

See Section 10.6.1.2, ÒUPM Refresh Timer Requests.Ó

1

RFEN

Refresh enable. Indicates that the UPM needs refresh services.

0 Refresh services are not required

1 Refresh services are required

See Section 10.3.8, Ò60x Bus-Assigned UPM Refresh Timer (PURT),Ó Section 10.3.9, ÒLocal

Bus-Assigned UPM Refresh Timer (LURT),Ó Section 10.3.10, Ò60x Bus-Assigned SDRAM

Refresh Timer (PSRT),Ó and Section 10.3.11, ÒLocal Bus-Assigned SDRAM Refresh Timer

(LSRT).У

2Р3

OP

Command opcode. Determines the command executed by the UPMx when a memory access

hit a UPM assigned bank.

00 Normal operation.

01 Write to array. On the next memory access that hits a UPM assigned bank, write the

contents of the MDR into the RAM location pointed by MAD. After the access, the MAD Þeld

is automatically incremented.

10 Read from array. On the next memory access that hits a UPM assigned bank, read the

contents of the RAM location pointed by MAD into the MDR. After the access, the MAD Þeld

is automatically incremented

11 Run pattern. On the next memory access that hits a UPM assigned bank, run the pattern

written in the RAM array. The pattern run starts at the location pointed by MAD and

continues until the LAST bit is set in the RAM.

Note: RLF determines the number of times a loop is executed during a pattern run.

4

Ñ

Reserved, should be cleared.

5Ð7

AMx

Address multiplex size. Determines how the address of the current memory cycle can be output

on the address pins. The address output on the pins controlled by the contents of the UPMx

RAM array. This Þeld is useful when connecting the MPC8260 to DRAM devices requiring row

and column addresses multiplexed on the same pins.

See Section 10.6.4.2, ÒAddress Multiplexing.У

8Р9

DSx

Disable timer period. Guarantees a minimum time between accesses to the same memory bank

if it is controlled by the UPMx. The disable timer is turned on by the TODT in the RAM array, and

when expired, the UPMx allows the machine access to handle a memory pattern to the same

memory region. Accesses to a different memory region by the same UPMx will be allowed.

00 1-cycle disable period

01 2-cycle disable period

10 3-cycle disable period

11 4-cycle disable period

Note: To avoid conßicts between successive accesses to different memory regions, the

minimum pattern in the RAM array for a request serviced should not be shorter than the period

established by DSx.