8 sdram read/write transactions, 9 sdram mode-set command timing, Sdram read/write transactions -46 – Motorola MPC8260 User Manual

Page 322: Sdram mode-set command timing -46, 9 sdram m, Command timing

10-46

MPC8260 PowerQUICC II UserÕs Manual

MOTOROLA

Part III. The Hardware Interface

10.4.8 SDRAM Read/Write Transactions

The SDRAM interface supports the following read/write transactions:

¥

Single-beat reads/writes up to double word size

¥

Bursts of two, three, or four double words

SDRAM devices perform bursts for each transaction, the burst length depends on the port

size. For 64-bit port size, it is a burst of 4. For 32-bit port size, it is a burst of 8. For reads

that require less than the full burst length, extraneous data in the burst is ignored. For writes

that require less than the full burst length, the MPC8260 protects non-targeted addresses by

driving DQMn high on the irrelevant cycles of the burst. However, system performance is

not compromised since, if a new transaction is pending, the MPC8260 begins executing it

immediately, effectively terminating the burst early.

10.4.9 SDRAM M

ODE

-S

ET

Command Timing

The MPC8260 transfers mode register data (CAS latency, burst length, burst type) stored

in P/LSDMR[SDMODE] to the SDRAM array by issuing the

MODE

-

SET

command.

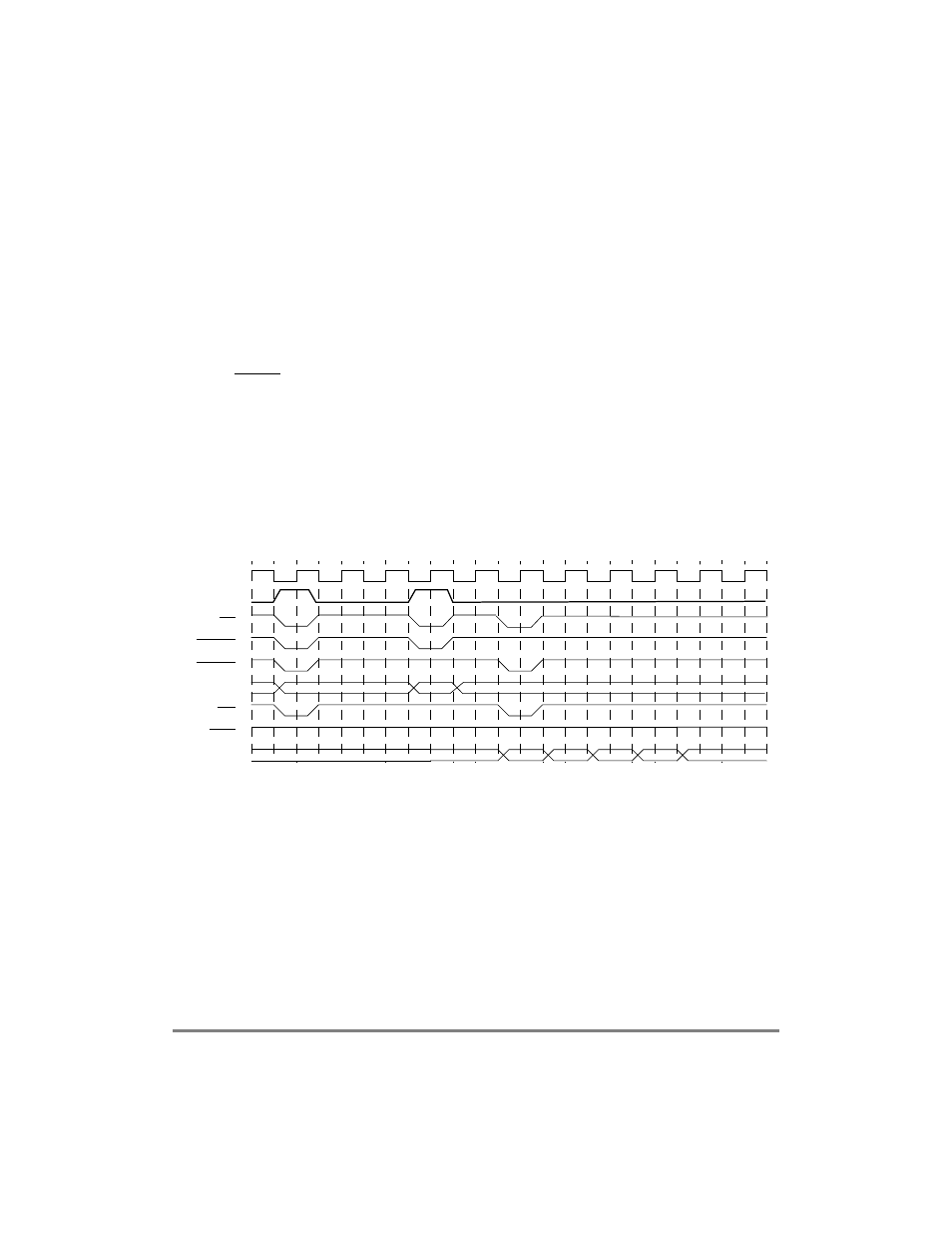

Figure 10-37 shows timing for the

MODE

-

SET

command.

Figure 10-37. SDRAM M

ODE

-S

ET

Command Timing

Figure 10-38 shows mode data bit settings.

CLK

ALE

CS

SDRAS

SDCAS

MA[0Ð11]

WE

DQM

Data

Z

Z

D0

D1

D2

D3

*Mode Data

Row

Column

*The mode data is the address value during a mode-set cycle. It is driven by the memory controller, in single

MPC8260 mode, according to P/LSDMR[CL] register. In 60x-compatible mode, software must drive the correct

value on the address lines. Figure 10-38 shows the actual value.

Mode Set

Page Activate

Write (Burst)