2 idmax parameter ram, Idmax parameter ram -16, 2 idma x parameter ram – Motorola MPC8260 User Manual

Page 540

18-16

MPC8260 PowerQUICC II UserÕs Manual

MOTOROLA

Part IV. Communications Processor Module

18.8.2 IDMAx Parameter RAM

When an IDMAx channel is conÞgured to auto buffer or buffer chaining mode, the

MPC8260 uses the IDMAx parameters listed in the Table 18-4. Parameters should be

modiÞed only while the channel is disabled, that is, before the Þrst

START

_

IDMA

command

or when the event registerÕs stop-completed bit (IDSR[SC]) is set following a

STOP

_

IDMA

command.

Each IDMAx channel parameter table can be placed at any 64-byte aligned address in the

dual-port RAMÕs general-purpose area (banks 1Ð8). The CP accesses each IDMAx channel

parameter table using a user-programmed pointer (IDMAx_BASE) located in the

parameter RAM; see Section 13.5.2, ÒParameter RAM.Ó For example, if the IDMA1

channel parameter table is to be placed at address offset 0x2000 in the dual-port RAM,

write 0x2000 to IDMA1_BASE.

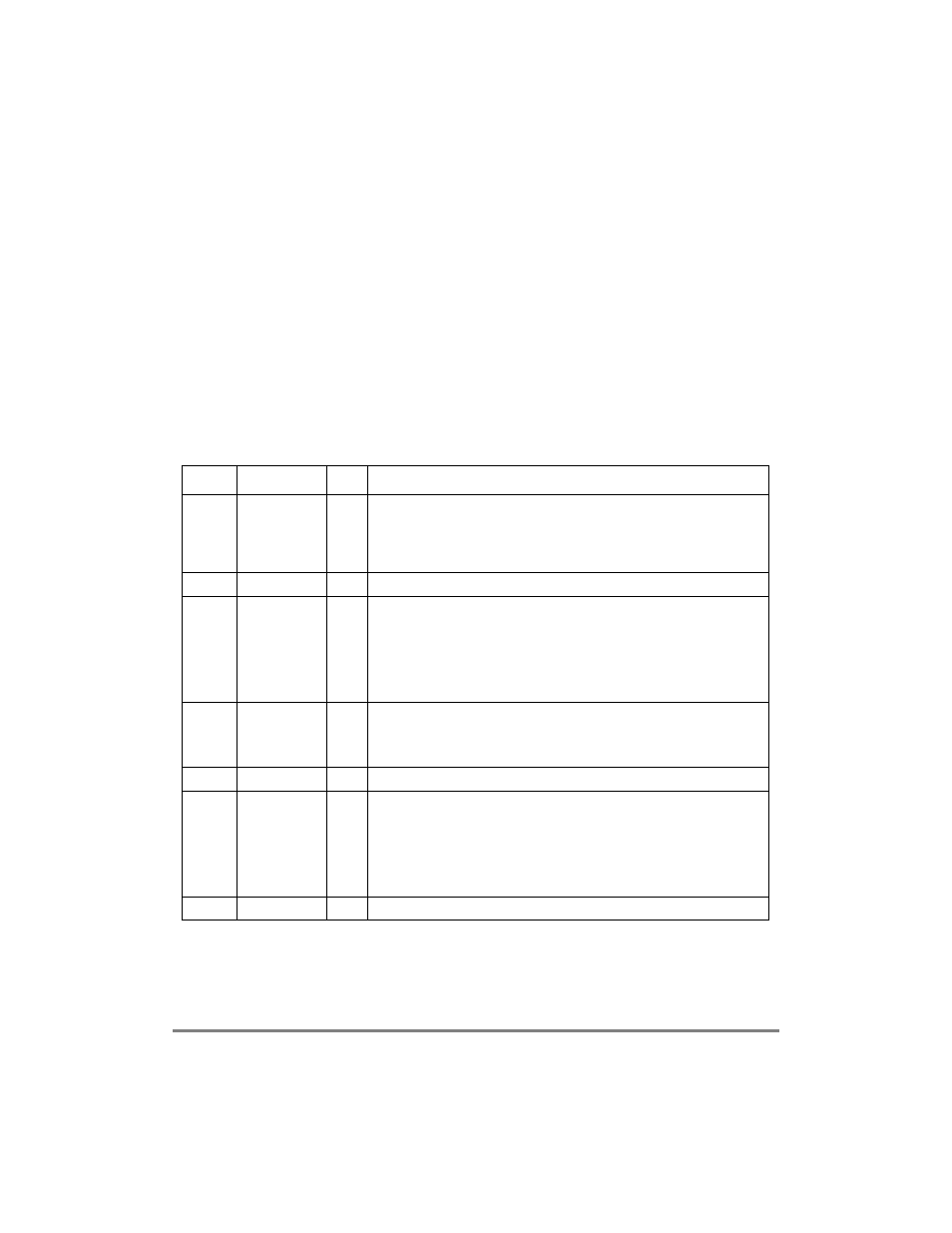

Table 18-4. IDMAx Parameter RAM

Offset

1

Name

Width

Description

0x00

IBASE

Hword IDMA BD table base address. DeÞnes the starting location in the dual-port RAM

for the set of IDMA BDs. It is an offset from the beginning of the dual-port RAM.

The user must initialize IBASE before enabling the IDMA channel and should

not overlap BD tables of two enabled serial controllers or IDMA channels or

erratic operation results. The IBASE value should be 16-bit aligned.

0x02

DCM

Hword DMA channel mode. See Section 18.8.2.1, ÒDMA Channel Mode (DCM).Ó

0x04

IBDPTR

Hword IDMA BD pointer. Points to the current BD during transfer processing. Points to

the next BD to be processed when an idle channel is restarted. Initialize to

IBASE before the Þrst

START

_

IDMA

command. If BD[W] = 1, the CP initializes

IBPTR to IBASE When the end of an IDMA BD table is reached. After a

STOP

_

IDMA

command is issued, IBDPTR points to the next BD to be processed.

It can be modiÞed after SC interrupt is set and before a

START

_

IDMA

command is

reissued.

0x06

DPR_BUF

Hword IDMA transfer buffer base address. The base address should be aligned

according to the buffer size determined by DCM[DMA_WRAP]. The transfer

buffer size should be consistent with DCM[DMA_WRAP]; that is, DPR_BUF =

(64 X 2

DMA_WRAP

) - 32. See Section 18.8.2.1, ÒDMA Channel Mode (DCM).Ó

0x08

BUF_INV

Hword Internal buffer inventory. Indicates the quantity of data inside the internal buffer.

0x0A

SS_MAX

Hword Steady-state maximum transfer size in bytes. User-deÞned parameter to

increase microcode efÞciency. Initialize to internal_buffer_size - 32, that is,

SS_MAX = (64 X 2

DMA_WRAP

) - 32. If possible, SS_MAX is used as the transfer

size on transfers to/from memory in memory-to-peripheral mode or in

peripheral-to-memory mode. For memory-to-memory mode, SS_MAX is used

as the transfer size for at least one of the devices. SS_MAX should be

consistent with STS, DTS, and DCM[S/D]. See Table 18-7 and Table 18-8.

0x0C

DPR_IN_PTR

Hword Write pointer inside the internal buffer.