1 requests, Requests -64, Ram array indexing -64 – Motorola MPC8260 User Manual

Page 340

10-64

MPC8260 PowerQUICC II UserÕs Manual

MOTOROLA

Part III. The Hardware Interface

Note that 60x bus accesses that hit a bank allocated to the local bus are transferred to the

local bus. However, local bus accesses that hit a bank allocated to the 60x bus are ignored.

10.6.1 Requests

An internal or external deviceÕs request for a memory access initiates one of the following

patterns (MxMR[OP] = 00):

¥

Read single-beat pattern (RSS)

¥

Read burst cycle pattern (RBS)

¥

Write single-beat pattern (WSS)

¥

Write burst cycle pattern (WBS)

These patterns are described in Section 10.6.1.1, ÒMemory Access Requests.Ó

A UPM refresh timer request pattern initiates a refresh timer pattern (PTS), as described in

Section 10.6.1.2, ÒUPM Refresh Timer Requests.Ó

An exception (caused by a soft reset or the assertion of TEA) occurring while another UPM

pattern is running initiates an exception condition pattern (EXS).

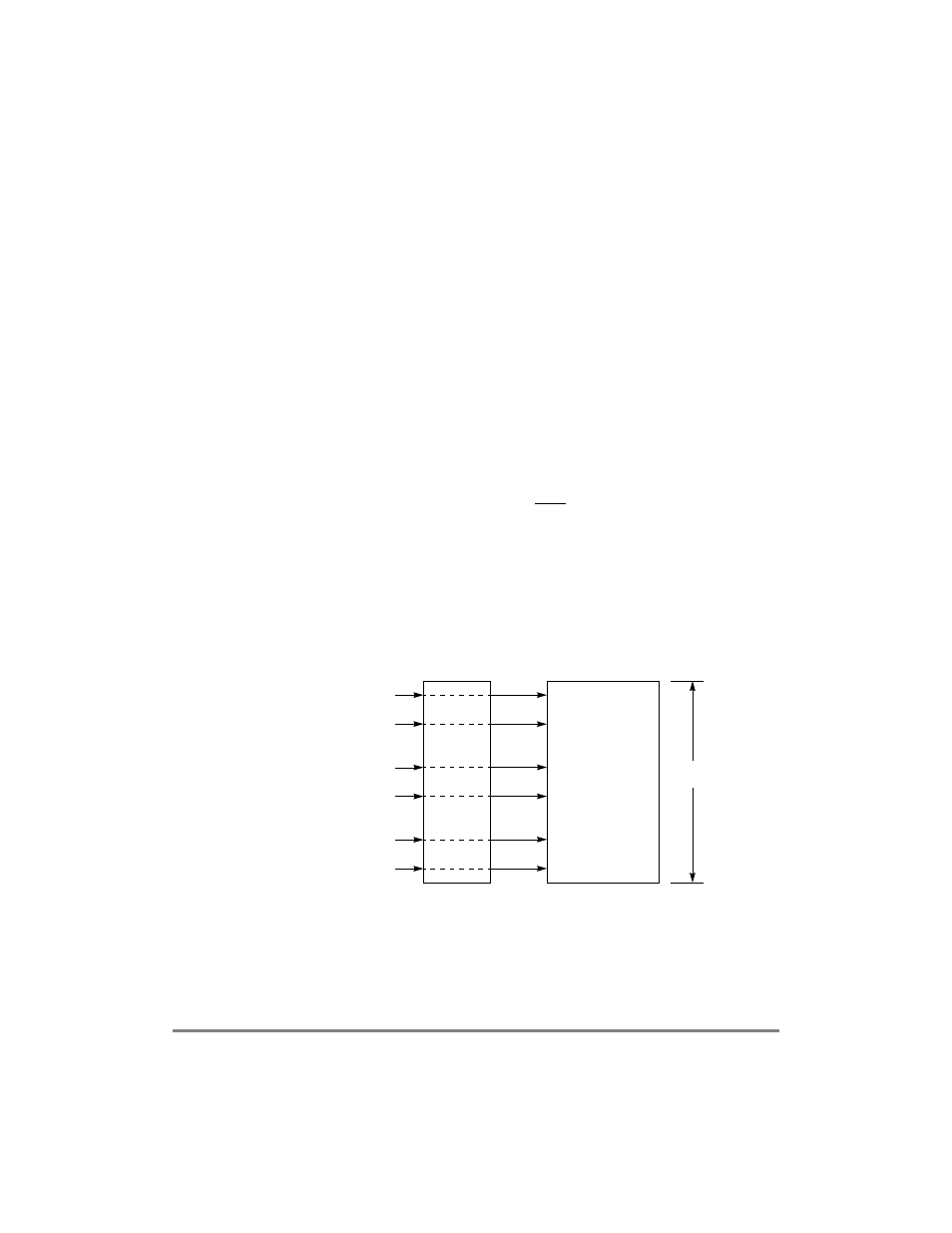

A special pattern in the RAM array is associated with each of these cycle type. Figure 10-56

shows the start addresses of these patterns in the UPM RAM, according to cycle type.

RUN

commands (MxMR[OP] = 11), however, can initiate patterns starting at any of the 64 UPM

RAM words.

Figure 10-56. RAM Array Indexing

Write Single-Beat Request

Read Burst Request

Read Single-Beat Request

Write Burst Request

RAM Array

Refresh Timer Request

Exception Condition Request

RSS

RBS

WSS

WBS

PTS

EXS

64 RAM

Words

Array Index

Generator