8 scc bisync dle register (bdle), Scc bisync dle register (bdle) -8, Bisync dle (bdle) -8 – Motorola MPC8260 User Manual

Page 640: Bsync field descriptions -8, See section 22.8, òscc bisync dle register (bdle), Table 22-5 describes bsync þelds

22-8

MPC8260 PowerQUICC II UserÕs Manual

MOTOROLA

Part IV. Communications Processor Module

Table 22-5 describes BSYNC Þelds.

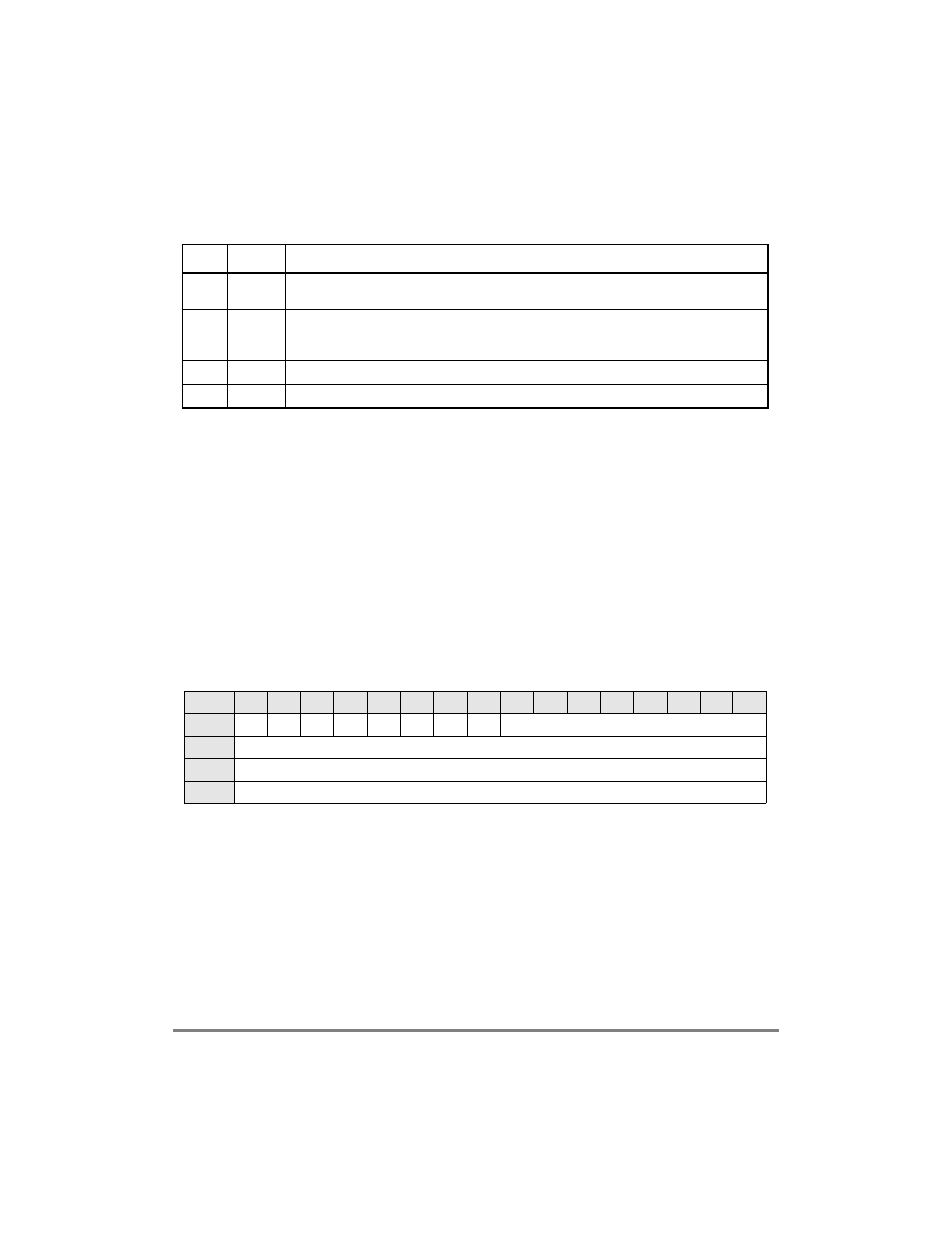

22.8 SCC BISYNC DLE Register (BDLE)

The BDLE register is used to deÞne the BISYNC stripping and insertion of DLE characters.

When an underrun occurs while a message is being sent in transparent mode, the BISYNC

controller inserts DLE-SYNC pairs until the next buffer is available for transmission.

In transparent mode, the receiver discards any DLE character received and excludes it from

the BCS if the valid bit (BDLE[V]) is set. If the second character is SYNC, the controller

discards it and excludes it from the BCS. If it is a DLE, the controller writes it to the buffer

and includes it in the BCS. If it is not a DLE or SYNC, the controller examines the control

character table and acts accordingly. If the character is not in the table, the buffer is closed

with the DLE follow character error bit set. If the valid bit is not set, the receiver treats the

character as a normal character. When using 7-bit characters with parity, the parity bit

should be included in the DLE register value.

Table 22-5. BSYNC Field Descriptions

Bits

Name Description

0

V

Valid. If V = 1 and the receiver is not in hunt mode when a SYNC character is received, this

character is discarded.

1

DIS

Disable BSYNC stripping

0 Normal mode.

1 BSYNC stripping disabled (BISYNC transparent mode only).

2Р7

С

All zeroes

8Ð15

SYNC

SYNC character

Bit

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

Field

V

DIS

0

0

0

0

0

0

DLE

Reset

UndeÞned

R/W

R/W

Address

SCC Base + 0x40

Figure 22-4. BISYNC DLE (BDLE)