Brgcx field descriptions -3 – Motorola MPC8260 User Manual

Page 511

MOTOROLA

Chapter 16. Baud-Rate Generators (BRGs)

16-3

Part IV. Communications Processor Module

Table 16-1 describes the BRGCx Þelds.

Table 16-2 shows the possible external clock sources for the BRGs.

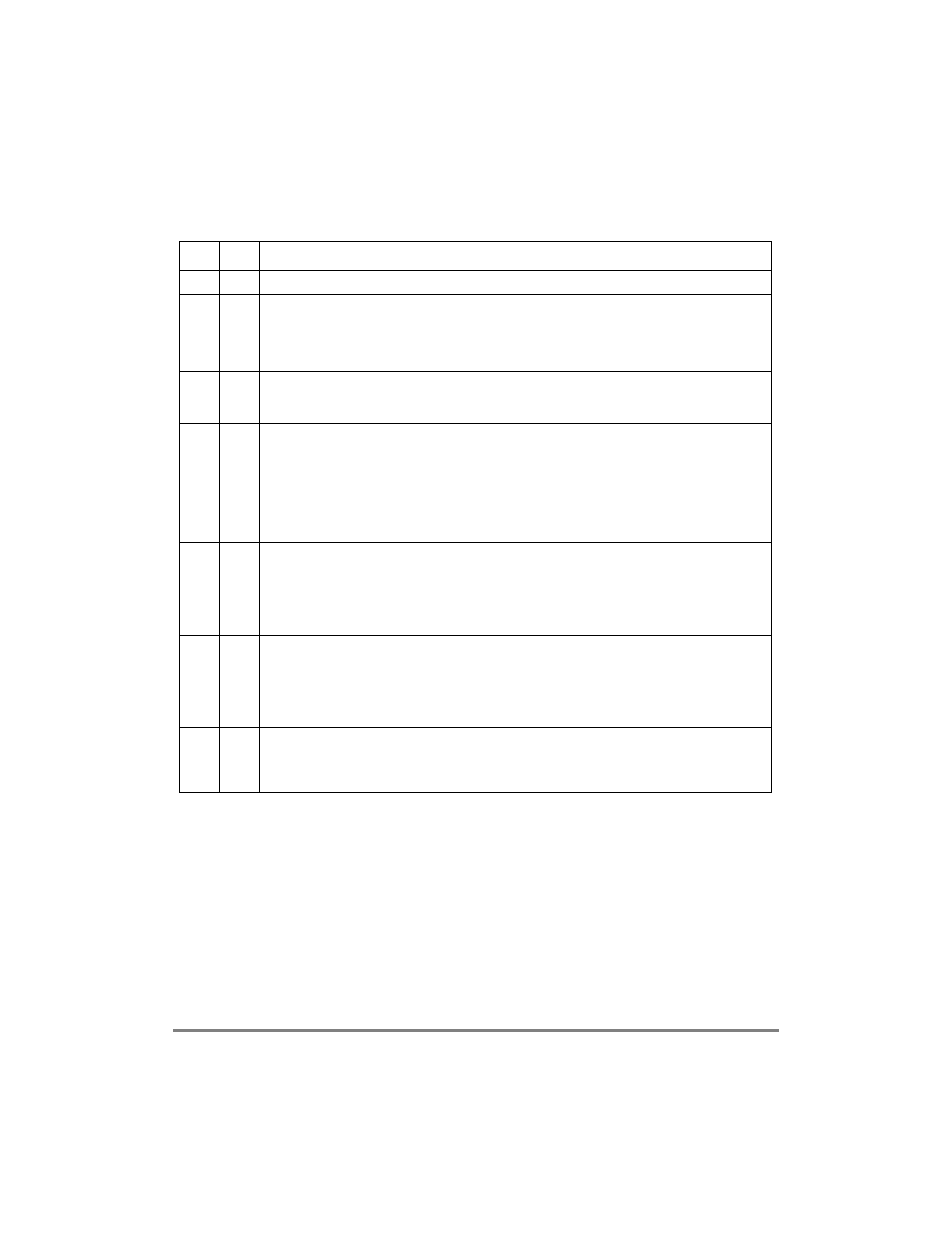

Table 16-1. BRGCx Field Descriptions

Bits

Name

Description

0Р13

С

Reserved, should be cleared.

14

RST

Reset BRG. Performs a software reset of the BRG identical to that of an external reset. A reset

disables the BRG and drives BRGO high. This is externally visible only if BRGO is connected to the

corresponding parallel I/O pin.

0 Enable the BRG.

1 Reset the BRG (software reset).

15

EN

Enable BRG count. Used to dynamically stop the BRG from countingÑuseful for low-power modes.

0 Stop all clocks to the BRG.

1 Enable clocks to the BRG.

16Ð17 EXTC

External clock source. Selects the BRG input clock. See Table 16-2.

00 The BRG input clock comes from the BRGCLK (internal clock generated from the CPM clock); see

Section 9.8, ÒSystem Clock Control Register (SCCR).Ó

01 If BRG1, 2, 5, 6: The BRG input clock comes from the CLK3 pin.

If BRG3, 4, 7, 8: The BRG input clock comes from the CLK9 pin

10 If BRG1, 2, 5, 6: The BRG input clock comes from the CLK5 pin.

If BRG3, 4, 7, 8: The BRG input clock comes from the CLK15 pin

11 Reserved.

18

ATB

Autobaud. Selects autobaud operation of the BRG on the corresponding RXD. ATB must remain zero

until the SCC receives the three Rx clocks. Then the user must set ATB to obtain the correct baud rate.

After the baud rate is obtained and locked, it is indicated by setting AB in the UART event register.

0 Normal operation of the BRG.

1 When RXD goes low, the BRG determines the length of the start bit and synchronizes the BRG to

the actual baud rate.

19Ð30 CD

Clock divider. CD presets an internal 12-bit counter that is decremented at the DIV16 output rate.

When the counter reaches zero, it is reloaded with CD. CD = 0xFFF produces the minimum clock rate

for BGRO (divide by 4,096); CD = 0x000 produces the maximum rate (divide by 1). When dividing by

an odd number, the counter ensures a 50% duty cycle by asserting the terminal count once on clock

low and next on clock high. The terminal count signals counter expiration and toggles the clock. See

Section 16.3, ÒUART Baud Rate Examples.Ó

31

DIV16 Divide-by-16. Selects a divide-by-1 or divide-by-16 prescaler before reaching the clock divider. See

Section 16.3, ÒUART Baud Rate Examples.Ó

0 Divide by 1.

1 Divide by 16.