3 exception priorities, 6 memory management, Exception priorities -26 – Motorola MPC8260 User Manual

Page 114: Memory management -26

2-26

MPC8260 PowerQUICC II UserÕs Manual

MOTOROLA

Part I. Overview

2.5.3 Exception Priorities

The exception priorities for the processor core are unchanged from those described in the

MPC603e UserÕs Manual except for the alignment exception, whose causes are prioritized

as follows:

1. Floating-point operand not word-aligned

2. lmw, stmw, lwarx, or stwcx. operand not word-aligned

3. eciwx or ecowx operand misaligned

4. A multiple or string access is attempted with MSR[LE] set

2.6 Memory Management

The following subsections describe the memory management features of the PowerPC

architecture and the MPC8260 implementation.

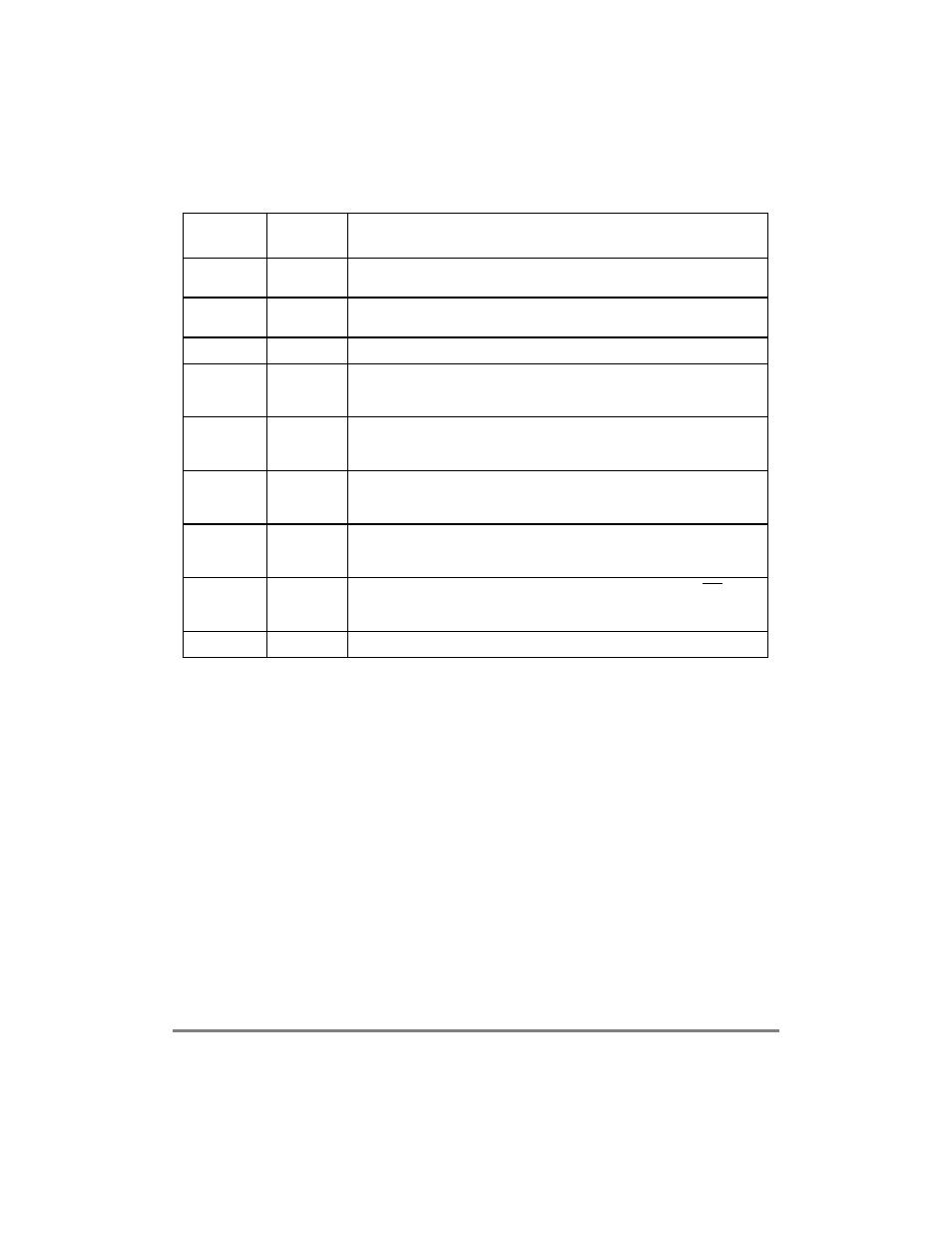

Trace

00D00

A trace exception is taken when MSR[SE] = 1 or when the currently completing

instruction is a branch and MSR[BE] = 1.

Floating-point

assist

00E00

Not implemented.

Reserved

00E10Ð00FFF Ñ

Instruction

translation

miss

01000

An instruction translation miss exception is caused when the effective address for

an instruction fetch cannot be translated by the ITLB.

Data load

translation

miss

01100

A data load translation miss exception is caused when the effective address for a

data load operation cannot be translated by the DTLB.

Data store

translation

miss

01200

A data store translation miss exception is caused when the effective address for a

data store operation cannot be translated by the DTLB, or when a DTLB hit occurs,

and the changed bit in the PTE must be set due to a data store operation.

Instruction

address

breakpoint

01300

An instruction address breakpoint exception occurs when the address (bits 0Ð29) in

the IABR matches the next instruction to complete in the completion unit, and the

IABR enable bit (bit 30) is set.

System

management

interrupt

01400

A system management interrupt is caused when MSR[EE] = 1 and the SMI input

signal is asserted.

Reserved

01500Ð02FFF

Ñ

Table 2-5. Exceptions and Conditions (Continued)

Exception

Type

Vector Offset

(hex)

Causing Conditions