Hardware implementation register 1 (hid1) -15, Hid1 field descriptions -15, Hid2 field descriptions -15 – Motorola MPC8260 User Manual

Page 103: Table 2-3 describes the hid2 þelds

MOTOROLA

Chapter 2. PowerPC Processor Core

2-15

Part I. Overview

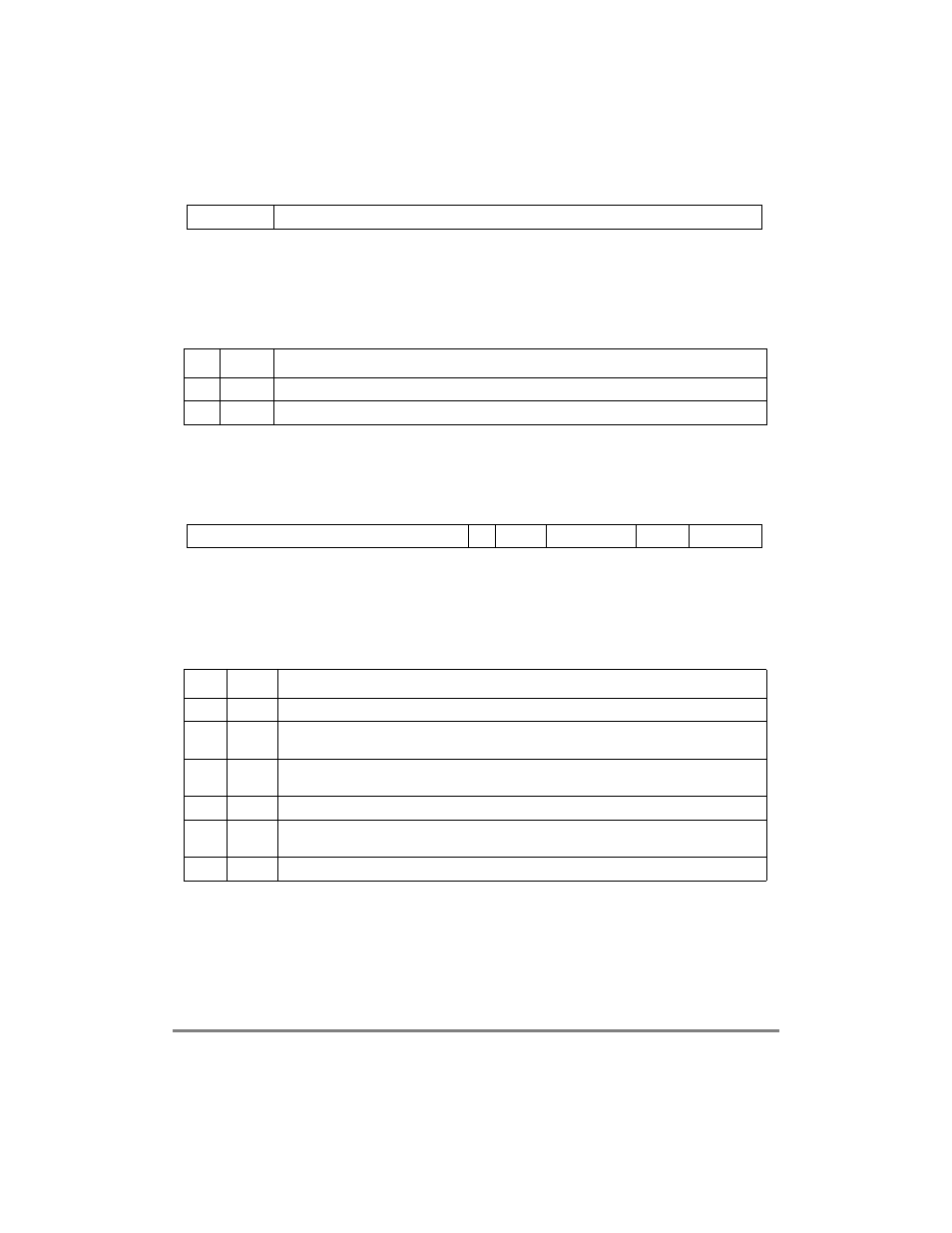

Figure 2-4. Hardware Implementation Register 1 (HID1)

Table 2-2 shows the bit deÞnitions for HID1.

2.3.1.2.3 Hardware Implementation-Dependent Register 2 (HID2)

The processor core implements an additional hardware implementation-dependent register

not described in the MPC603e UserÕs Manual, shown in Figure 2-5.

Figure 2-5. Hardware Implementation-Dependent Register 2 (HID2)

Table 2-3 describes the HID2 Þelds.

Table 2-2. HID1 Field Descriptions

Bits

Name

Function

0Ð4

PLLCFG PLL conÞguration setting

5Р31

С

Reserved

Table 2-3. HID2 Field Descriptions

Bits

Name

Function

0Р14

С

Reserved

15

SFP

Speed for low power. Setting SFP reduces power consumption at the cost of reducing the

maximum frequency, which beneÞts power-sensitive applications that are not frequency-critical.

16Ð18

IWLCK

Instruction cache way lock. Useful for locking blocks of instructions into the instruction cache for

time-critical applications that require deterministic behavior. See Section 2.4.2.3, ÒCache Locking.У

19Р23

С

Reserved

24Ð26

DWLCK Data cache way lock. Useful for locking blocks of data into the data cache for time-critical

applications where deterministic behavior is required. See Section 2.4.2.3, ÒCache Locking.У

27Р31

С

Reserved

0

4

5

31

Ñ

PLLCFG

0

14 15 16

18 19

23 24

26 27

31

SFP

IWLCK

DWLCK

С

С

С