Motorola MPC8260 User Manual

Page 126

3-6

MPC8260 PowerQUICC II UserÕs Manual

MOTOROLA

Part I. Overview

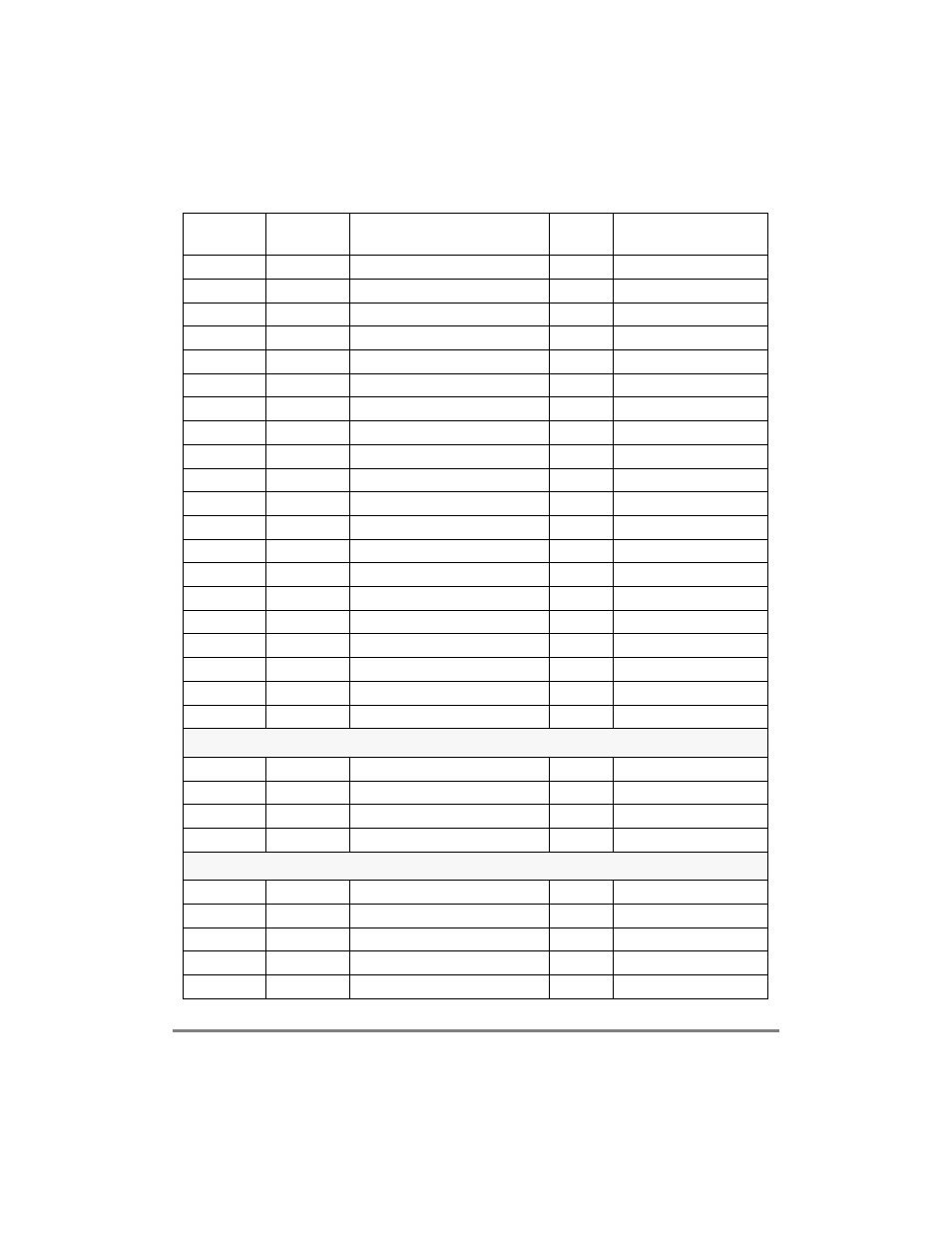

10D92

TMR2

Timer 2 mode register

16 bits

10D94

TRR1

Timer 1 reference register

16 bits

10D96

TRR2

Timer 2 reference register

16 bits

10D98

TCR1

Timer 1 capture register

16 bits

10D9A

TCR2

Timer 2 capture register

16 bits

10D9C

TCN1

Timer 1 counter

16 bits

10D9E

TCN2

Timer 2 counter

16 bits

10DA0

TMR3

Timer 3 mode register

16 bits

10DA2

TMR4

Timer 4 mode register

16 bits

10DA4

TRR3

Timer 3 reference register

16 bits

10DA6

TRR4

Timer 4 reference register

16 bits

10DA8

TCR3

Timer 3 capture register

16 bits

10DAA

TCR4

Timer 4 capture register

16 bits

10DAC

TCN3

Timer 3 counter

16 bits

10DAE

TCN4

Timer 4 counter

16 bits

10DB0

TER1

Timer 1 event register

16 bits

10DB2

TER2

Timer 2 event register

16 bits

10DB4

TER3

Timer 3 event register

16 bits

10DB6

TER4

Timer 4 event register

16 bits

10D74Ð11017

Reserved

Ñ

670 bytes

Ñ

SDMAÐGeneral

11018

SDSR

SDMA status register

8 bits

11019

Reserved

Ñ

24 bits

Ñ

1101C

SDMR

SDMA mask register

8 bits

1101D

Reserved

Ñ

24 bits

Ñ

IDMA

11020

IDSR1

IDMA 1 event register

8 bits

11021

Reserved

Ñ

24 bits

Ñ

11024

IDMR1

IDMA 1 mask register

8 bits

11025

Reserved

Ñ

24 bits

Ñ

11028

IDSR2

IDMA 2 event register

8 bits

Table 3-1. Internal Memory Map (Continued)

Internal

Address

Abbreviation

Name

Size

Section/Page Number