2 sdma mask register (sdmr), Sdma mask register (sdmr) -4, Pdtem and ldtem field descriptions -4 – Motorola MPC8260 User Manual

Page 528

18-4

MPC8260 PowerQUICC II UserÕs Manual

MOTOROLA

Part IV. Communications Processor Module

18.2.2 SDMA Mask Register (SDMR)

The SDMA mask register (SDMR) is an 8-bit read/write register with the same bit format

as the SDMA status register. If an SDMR bit is 1, the corresponding interrupt in SDSR is

enabled. If the bit is zero, the corresponding interrupt in the status register is masked.

SDMR is cleared at reset. SDMR can be accessed at 0x1101C.

18.2.3 SDMA Transfer Error Address Registers (PDTEA and LDTEA)

There are two 32-bit, read-only SDMA address registers. The PDTEA holds the system

address accessed during an SDMA transfer error on the 60x bus. The LDTEA holds the

system address accessed during an SDMA transfer error on the local bus. Both registers are

undeÞned at reset. PDTEA can be accessed at 0x10050; LDTEA can be accessed at

0x10058.

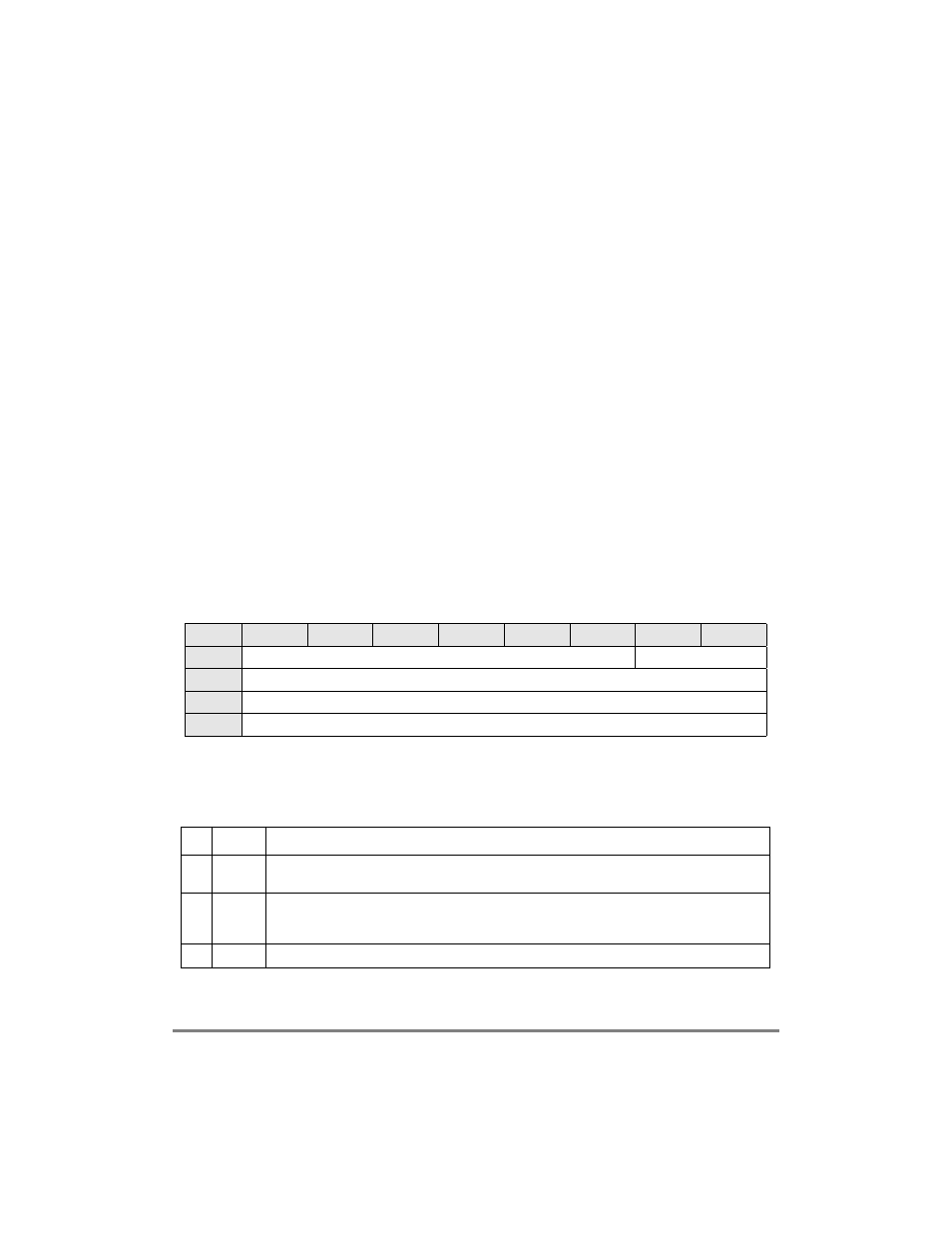

18.2.4 SDMA Transfer Error MSNUM Registers (PDTEM and LDTEM)

There are two SDMA transfer error MSNUM registers (PDTEM and LDTEM).

MSNUM[0Ð4] contains the sub-block code (SBC) used to identify the current peripheral

controller accessing the bus. MSNUM[5] identiÞes which half of the controller is

transferring (transmitter or receiver). The MSNUM of each transaction is held in these

registers until the transaction is complete.

PDTEM is for SDMA transfer errors on the 60x bus, and LDTEM is for errors on the local

bus. Both registers are undeÞned at reset. See Figure 18-4.

Table 18-2 describes PDTEM and LDTEM Þelds.

Bits

0

1

2

3

4

5

6

7

Field

MSNUM

Ñ

Reset

Ñ

R/W

R

Addr

0x10054 (PDTEM); 0x1005C (LDTEM)

Figure 18-4. SDMA Transfer Error MSNUM Registers (PDTEM/LDTEM)

Table 18-2. PDTEM and LDTEM Field Descriptions

Bits

Name

Description

0Ð4

MSNUM

[0Ð4]

Bits 0Ð4 of MSNUM is the sub-block code of the current peripheral controller accessing the bus. See

the SBC Þeld description of the CPCR in Section 13.4.1, ÒCP Command Register (CPCR).Ó

5

MSNUM

[5]

Bit 5 of MSNUM indicates which section of the peripheral controller is accessing the bus.

0 Transmit section

1 Receive section

6Р7

С

Reserved, should be cleared.