Using the swtr feature -12, Figure 14-8 sho ws how swtr can be used – Motorola MPC8260 User Manual

Page 466

14-12

MPC8260 PowerQUICC II UserÕs Manual

MOTOROLA

Part IV. Communications Processor Module

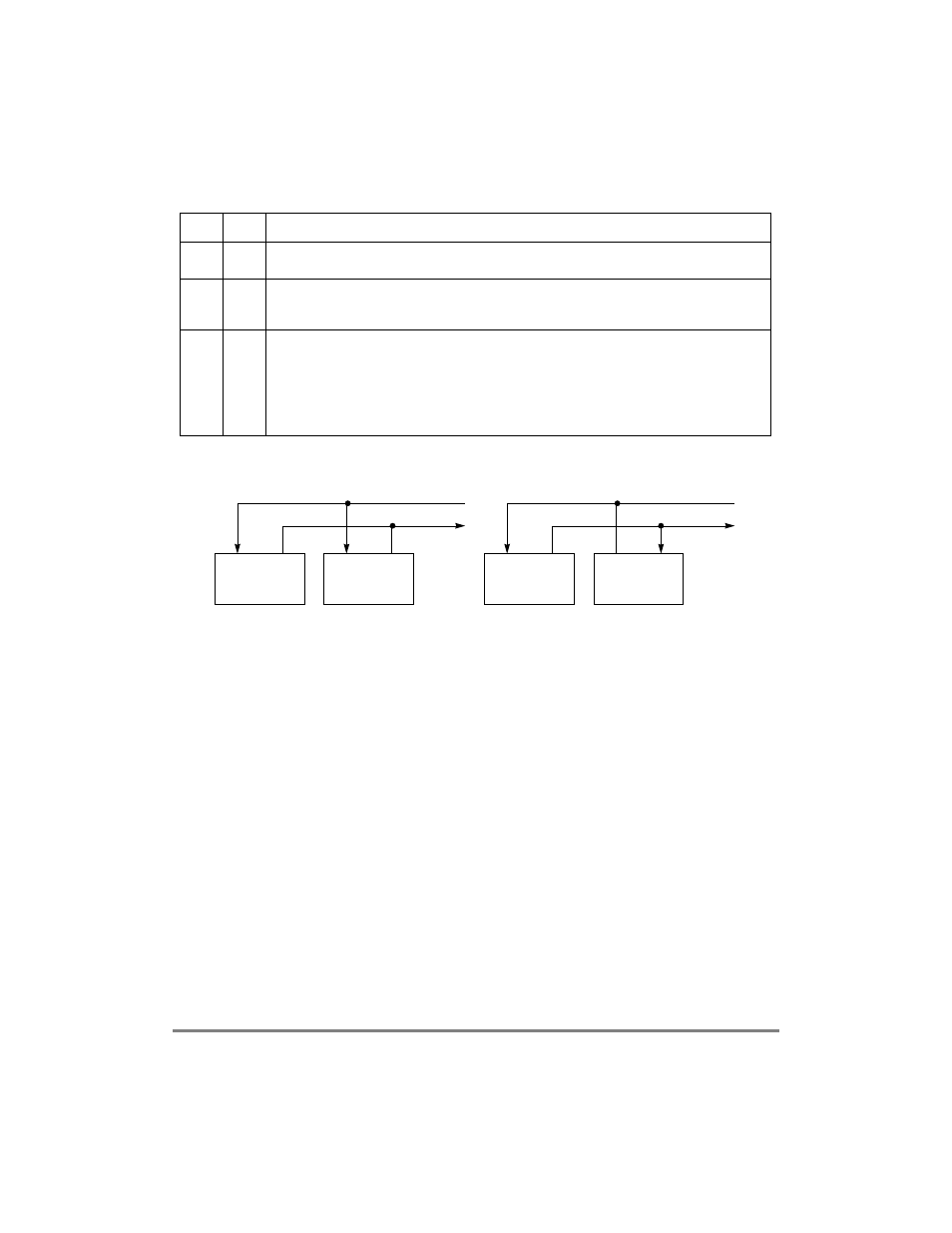

Figure 14-8 shows how SWTR can be used.

Figure 14-8. Using the SWTR Feature

The SWTR option lets station B listen to transmissions from station A and send data to

station A. To do this, station B would set SWTR in its receive route RAM. For this entry,

receive data is taken from the L1TXD pin and data is sent on the L1RXD pin. If the user

wants to listen only to station A transmissions and not send data on L1RXD, the CSEL bits

in the corresponding transmit route RAM entry should be cleared to prevent transmission

on the L1RXD pin.

Station B can transmit data to station A by setting the SWTR bit of the entry in its receive

route RAM. Data is sent on L1RXD rather than L1TXD, according to the transmit route

RAM. Note that this conÞguration could cause collisions with other data on L1RXD unless

an available (quiet) time slot is used. To transmit on L1RXD and not receive data on

L1TXD, clear the CSEL bits in the receive route RAM.

Note that if the transmit and receive sections of the TDM do not use a common clock

source, the SWTR feature can cause erratic behavior. Note also this feature does not work

with nibble operation.

11Ð13

CNT

Count. Indicates the number of bits/bytes (according to the BYT bit) that the routing and strobe select

of this entry controls. 000 = 1 bit/byte; 111= 8 bits/bytes.

14

BYT

Byte resolution

0 Bit resolution. The CNT value indicates the number of bits in this group.

1 Byte resolution. The CNT value indicates the number of bytes in this group.

15

LST

Last entry in the RAM. Whenever SI

x

RAM is used, LST must be set in one of the Tx or Rx entries of

each group. Even if all entries of a group are used, this bit must still be set in the last entry.

0 Not the last entry in this section of the route RAM.

1 Last entry in this RAM. After this entry, the SI waits for the sync signal to start the next frame.

Note that there must be only an even number of entries in an SI

x

RAM frame, because LST is active

only in odd-numbered entries (assuming the entry count starts with 0). Therefore, to obtain an even

number of entries, an entry may need to be split into two entries.

Table 14-1. SI

x

RAM Entry (MCC = 0) (Continued)

Bits

Name Description

Rx

Station A

Tx

Rx

Station B

Tx

L1TXD

L1RXD

Rx

Station A

Tx

Tx

Station B

Rx

L1TXD

L1RXD

Tx and Rx SIx RAMn[SWTR] = 1

Tx and Rx SIx RAMn[SWTR] = 0