5 spi parameter ram, Spi parameter ram -10, Spcomñspi command register -10 – Motorola MPC8260 User Manual

Page 934: Spcom field descriptions -10, Spi parameter ram memory map -10, Wn in figure 33-8, is used to start spi operation, Table 33-4 describes the spcom þelds

33-10

MPC8260 PowerQUICC II UserÕs Manual

MOTOROLA

Part IV. Communications Processor Module

Table 33-4 describes the SPCOM Þelds.

33.5 SPI Parameter RAM

The SPI parameter RAM area is similar to the SCC general-purpose parameter RAM. The

CP accesses the SPI parameter table using a user-programmed pointer (SPI_BASE) located

in the parameter RAM; see Section 13.5.2, ÒParameter RAM.Ó The SPI parameter table can

be placed at any 64-byte aligned address in the dual-port RAMÕs general-purpose area

(banks #1Ð#8). Some parameter values must be user-initialized before the SPI is enabled;

the CP initializes the others. Once initialized, parameter RAM values do not usually need

to be accessed. They should be changed only when the SPI is inactive. Table 33-5 shows

the memory map of the SPI parameter RAM.

Bit

0

1

2

3

4

5

6

7

Field

STR

Ñ

Reset

0000_0000

R/W

Write Only

Addr

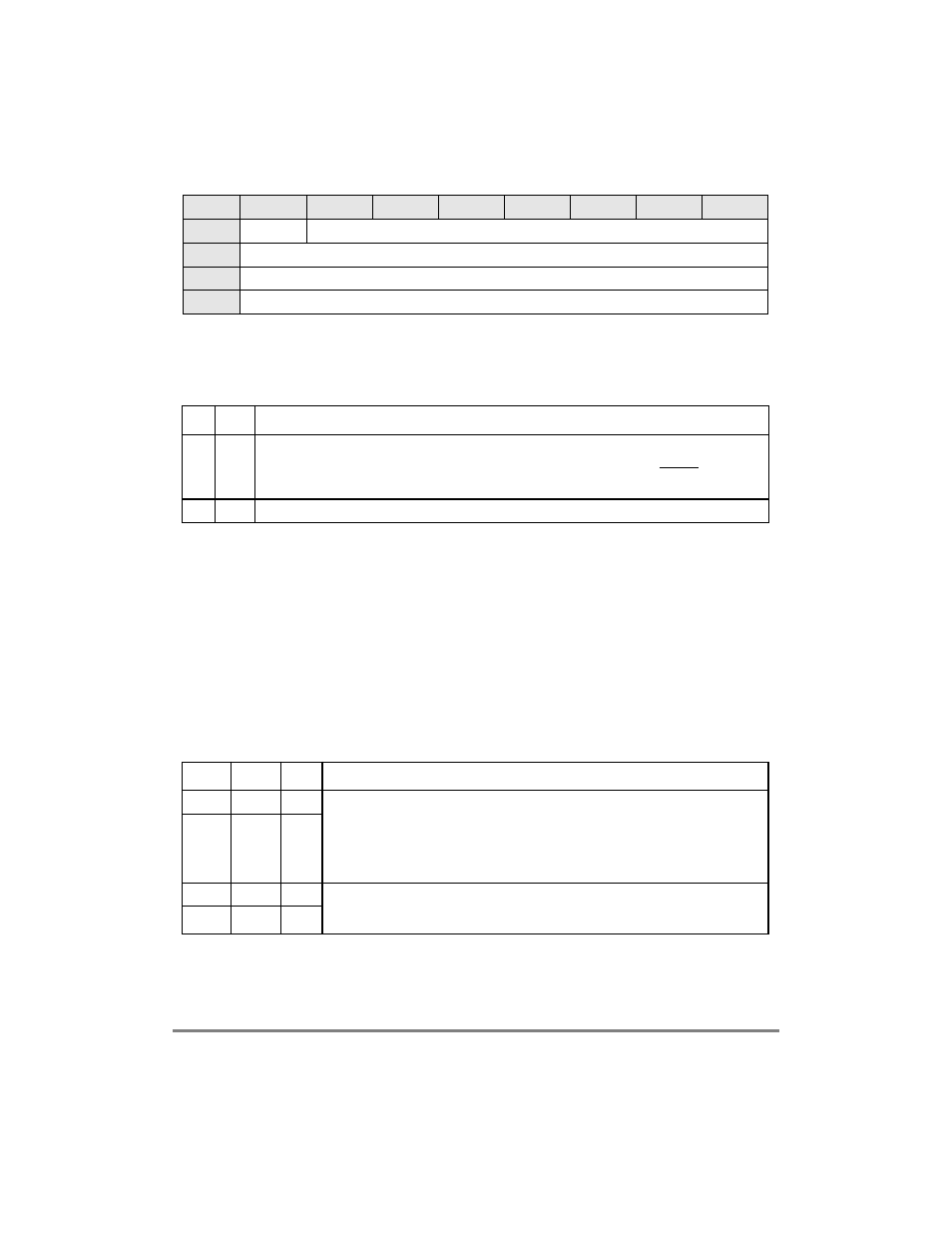

Figure 33-8. SPCOMÑSPI Command Register

Table 33-4. SPCOM Field Descriptions

Bits

Name

Description

0

STR

Start transmit. For an SPI master, setting STR causes the SPI to start transferring data to and from the

Tx/Rx buffers if they are prepared. For a slave, setting STR when the SPI is idle causes it to load the Tx

data register from the SPI Tx buffer and start sending with the next SPICLK after SPISEL is asserted.

STR is cleared automatically after one system clock cycle.

1Р7

С

Reserved and should be cleared.

Table 33-5. SPI Parameter RAM Memory Map

Offset

1

Name

Width

Description

0x00

RBASE

Hword Rx/Tx BD table base address. Indicate where the BD tables begin in the dual-port RAM.

Setting Rx/TxBD[W] in the last BD in each BD table determines how many BDs are

allocated for the Tx and Rx sections of the SPI. Initialize RBASE/TBASE before enabling

the SPI. Furthermore, do not conÞgure BD tables of the SPI to overlap any other active

controllerÕs parameter RAM.

RBASE and TBASE should be divisible by eight.

0x02

TBASE

Hword

0x04

RFCR

Byte

Rx/Tx function code registers. The function code registers contain the transaction

speciÞcation associated with SDMA channel accesses to external memory. See

Section 33.5.1, ÒReceive/Transmit Function Code Registers (RFCR/TFCR).Ó

0x05

TFCR

Byte