5 the smc in gci mode, 1 smc gci parameter ram, The smc in gci mode -30 – Motorola MPC8260 User Manual

Page 726: Smc gci parameter ram -30, Smc gci parameter ram memory map -30, Gci protocol is described in table 26-17

26-30

MPC8260 PowerQUICC II UserÕs Manual

MOTOROLA

Part IV. Communications Processor Module

26.5 The SMC in GCI Mode

The SMC can control the C/I and monitor channels of the GCI frame. When using the SCIT

conÞguration of a GCI, one SMC can handle SCIT channel 0 and the other can handle SCIT

channel 1. The main features of the SMC in GCI mode are as follows:

¥

Each SMC channel supports the C/I and monitor channels of the GCI (IOM-2) in

ISDN applications

¥

Two SMCs support both sets of C/I and monitor channels in SCIT channels 0 and 1

¥

Full-duplex operation

¥

Local loopback and echo capability for testing

To use the SMC GCI channels properly, the TSA must be conÞgured to route the monitor

and C/I channels to the preferred SMC. Chapter 14, ÒSerial Interface with Time-Slot

Assigner,Ó describes how to program this conÞguration. GCI mode is selected by setting

SMCMR[SM] to 0b10. Section 26.2.1, ÒSMC Mode Registers (SMCMR1/SMCMR2)Ó

describes other protocol-speciÞc SMCMR bits.

26.5.1 SMC GCI Parameter RAM

The GCI parameter RAM differs from that for UART and transparent mode. The CP

accesses each SMCÕs GCI parameter table using a user-programmed pointer

(SMCx_BASE) located in the parameter RAM; see Section 13.5.2, ÒParameter RAM.Ó

Each SMC GCI parameter RAM table can be placed at any 64-byte aligned address in the

dual-port RAMÕs general-purpose area (banks #1Ð#8). In GCI mode, parameter RAM

contains the BDs instead of pointers to them. Compare Table 26-17 with Table 26-2 to see

the differences. (In GCI mode, the SMC has no extra protocol-speciÞc parameter RAM.)

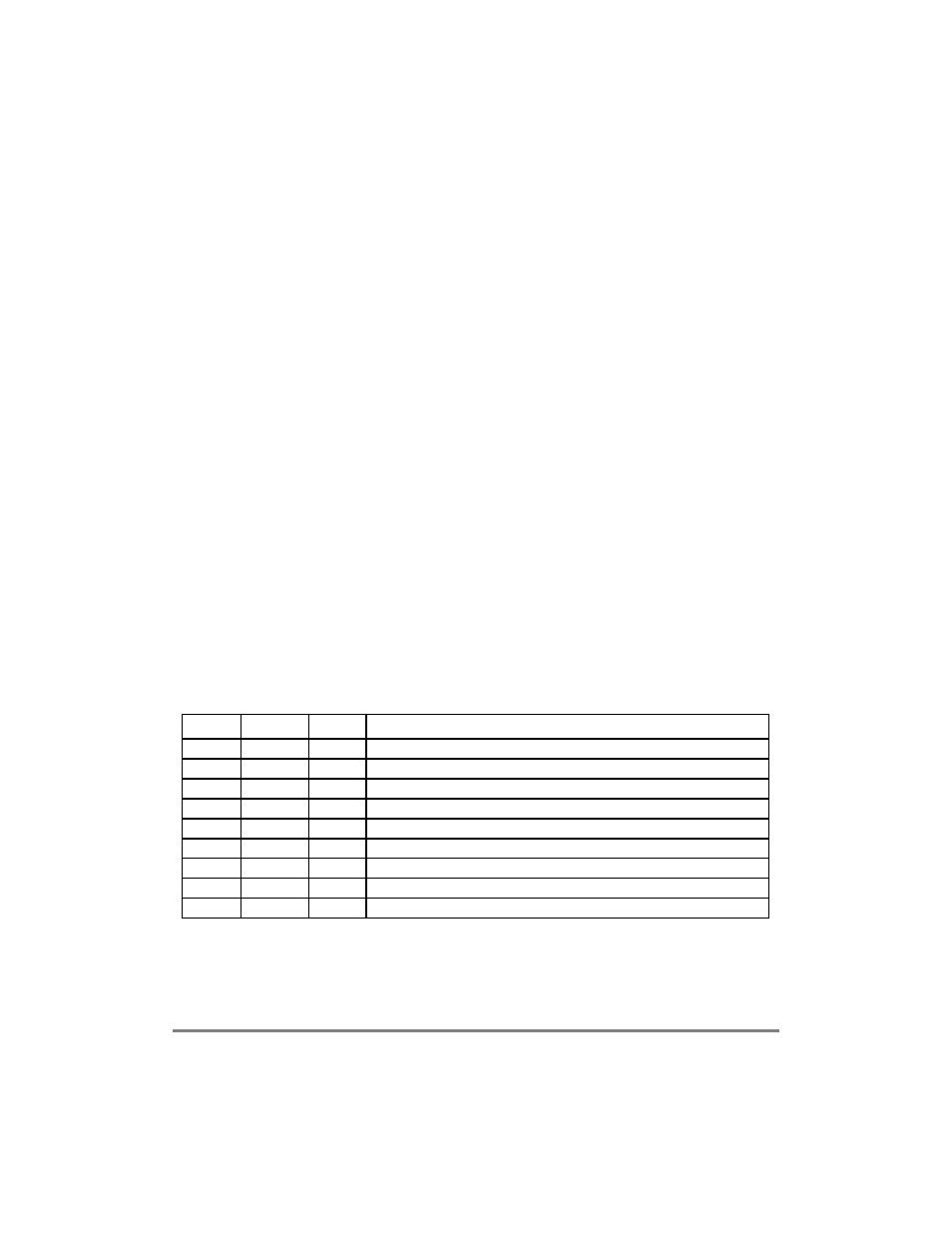

Table 26-17. SMC GCI Parameter RAM Memory Map

Offset

1

1

From the pointer value programmed in SMCx_BASE: SMC1_BASE at 0x87FC, SMC2_BASE at 0x88FC.

Name

Width

Description

0x00

M_RxBD

Half word

Monitor channel RxBD. See Section 26.5.5, ÒSMC GCI Monitor Channel RxBD.Ó

0x02

M_TxBD

Half word

Monitor channel TxBD. See Section 26.5.6, ÒSMC GCI Monitor Channel TxBD.Ó

0x04

CI_RxBD

Half word

C/I channel RxBD. See Section 26.5.7, ÒSMC GCI C/I Channel RxBD.Ó

0x06

CI_TxBD

Half word

C/I channel TxBD. See Section 26.5.8, ÒSMC GCI C/I Channel TxBD.Ó

0x08

RSTATE

2

2

RSTATE, M_RxD, M_TxD, CI_RxD, and CI_TxD do not need to be accessed by the user in normal operation,

and are reserved for RISC use only.

Word

Rx/Tx Internal State

0x0C

Half word

Monitor Rx Data

0x0E

Half word

Monitor Tx Data

0x10

CI_RxD

Half word

C/I Rx Data

0x12

CI_TxD

Half word

C/I Tx Data