Motorola MPC8260 User Manual

Page 128

3-8

MPC8260 PowerQUICC II UserÕs Manual

MOTOROLA

Part I. Overview

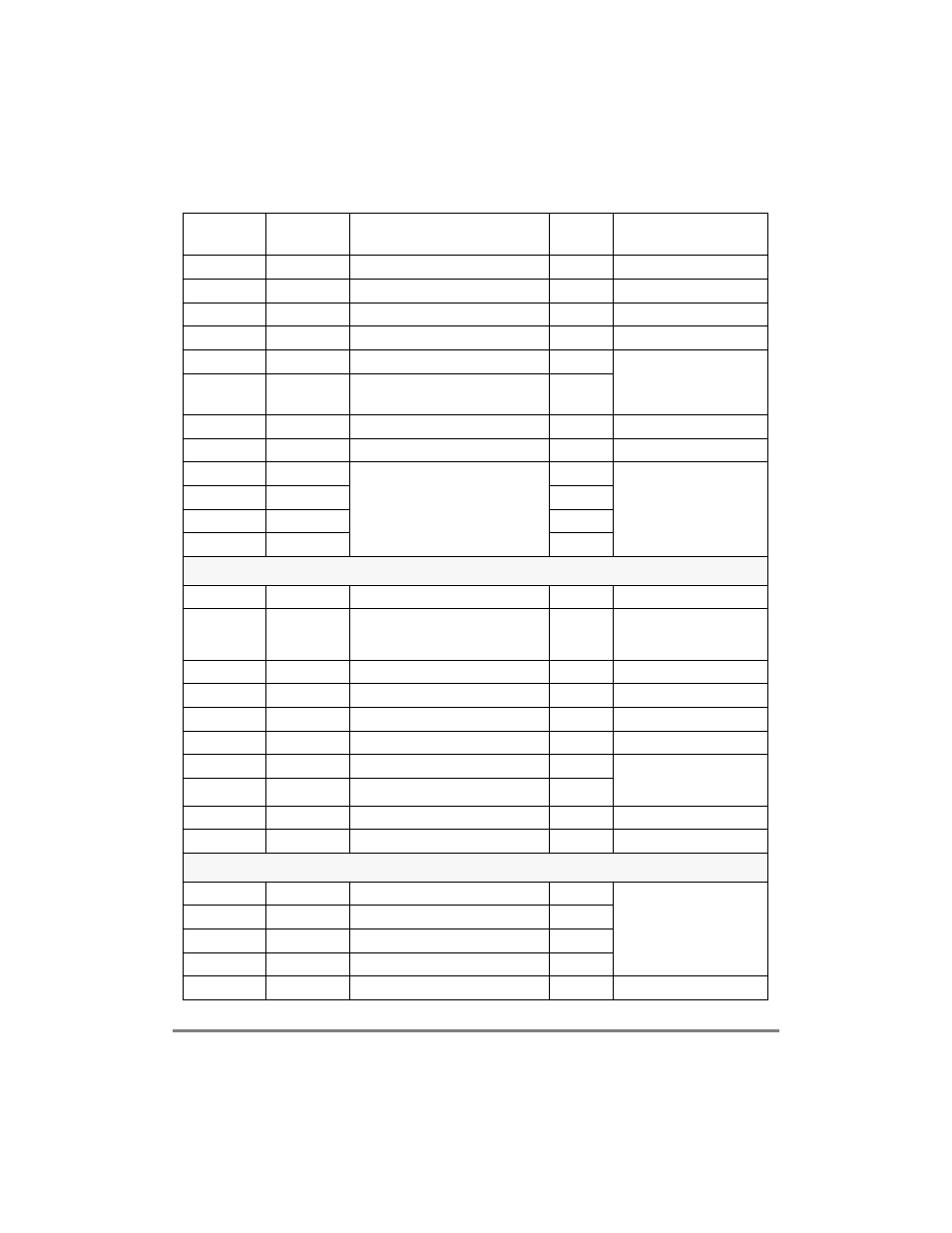

11328

FTODR2

FCC2 transmit on-demand register

16 bits

1132A

Reserved

Ñ

2 bytes

Ñ

1132C

FDSR2

FCC2 data synchronization register

16 bits

1132E

Reserved

Ñ

2 bytes

Ñ

11330

FCCE2

FCC2 event register

32 bits

29.13.3/29-87 (ATM)

30.18.2/30-21 (Ethernet)

31.9/31-14 (HDLC)

11334

FCCM2

FCC2 mask register

32 bits

11338

FCCS2

FCC2 status register

8 bits

11339

Reserved

Ñ

3 bytes

Ñ

1133C

FTIRR2_PHY0 FCC2 transmit internal rate registers

for PHY0Ð3

8 bits

1133D

FTIRR2_PHY1

8 bits

1133E FTIRR2_PHY2

8

bits

1133F

FTIRR2_PHY3

8 bits

FCC3

11340

GFMR3

FCC3 general mode register

32 bits

11344

FPSMR3

FCC3 protocol-speciÞc mode register

32 bits

29.13.2/29-85 (ATM)

30.18.1/30-20 (Ethernet)

31.6/31-7 (HDLC)

11348

FTODR3

FCC3 transmit on-demand register

16 bits

1134A

Reserved

Ñ

2 bytes

Ñ

1134C

FDSR3

FCC3 data synchronization register

16 bits

1134E

Reserved

Ñ

2 bytes

Ñ

11350

FCCE3

FCC3 event register

32 bits

29.13.3/29-87 (ATM)

30.18.2/30-21 (Ethernet)

31.9/31-14 (HDLC)

11354

FCCM3

FCC3 mask register

32 bits

11358

FCCS3

FCC3 status register

8 bits

11359Ð113FF

Reserved

Reserved

167 bytes

Ñ

BRGs 5Ð8

115F0

BRGC5

BRG5 conÞguration register

32 bits

115F4

BRGC6

BRG6 conÞguration register

32 bits

115F8

BRGC7

BRG7 conÞguration register

32 bits

115FC

BRGC8

BRG8 conÞguration register

32 bits

11600Ð1185F

Reserved

Reserved 608

bytes

Ñ

Table 3-1. Internal Memory Map (Continued)

Internal

Address

Abbreviation

Name

Size

Section/Page Number