4 internal receiver state (rstate), Internal receiver state (rstate) -11 – Motorola MPC8260 User Manual

Page 741

MOTOROLA

Chapter 27. Multi-Channel Controllers (MCCs)

27-11

Part IV. Communications Processor Module

27.6.4 Internal Receiver State (RSTATE)

Internal receiver state (RSTATE) is a 4-byte register that provides transaction parameters

associated with SDMA channel accesses (like function code registers) and starts the

receiver channel.

To start the channel the user must write 0xHH800000 to RSTATE, where HH is the

RSTATE high byte (see Figure 27-9). When the channel is active the CP changes the value

of the 3 LSBs, hence these 3 bytes must be masked if the user reads back the RSTATE.

3

IDLM

Idle mode.

0 No idle patterns are sent between frames. After sending NOF+1 ßags, the transmitter starts

sending the data of the frame. If the transmission is between frames and the frame buffers are not

ready, the transmitter sends ßags until it can start transmitting the data.

1 At least one idle pattern is sent between adjacent frames. The NOF value shall be no smaller than

the PAD setting, see TxBD. If NOF = 0, this is identical to ßag sharing in HDLC. Mode ßags

precede the actual data. When IDLM = 1, at least one idle pattern is sent between adjacent

frames. If the transmission is between frames and the frame buffer is not ready, the transmitter

sends idle characters. When data is ready, the NOF+1 ßags are sent followed by the data frame.

If IDLE mode is selected and NOF = 1, the following sequence is sent:

......init value, FF, FF, ßag, ßag, data, ........

The init value before the idle will be ones.

4Р7

С

These bits must be cleared.

8

CRC

Selects the type of CRC when HDLC channel mode is used.

0 16-bit CCITT-CRC

1 32-bit CCITT-CRC

9

Ñ

This bit must be cleared.

10

TS

Receive time stamp. If this bit is set a 4 byte time stamp is written at the beginning of every data

buffer that the BD points to.If this bit is set the data buffer must start from an address equal to 8*n-4

(n is any integer larger than 0).

11Ð12 RQN

Receive queue number. SpeciÞes the receive interrupt queue number.

00 Queue number 0.

01 Queue number 1.

10 Queue number 2.

11 Queue number 3.

13Ð15 NOF

Number of ßags. NOF deÞnes the minimum number of ßags before frames:

000 At least 1 ßag

001 At least 2 ßags

....

111 At least 8 ßags

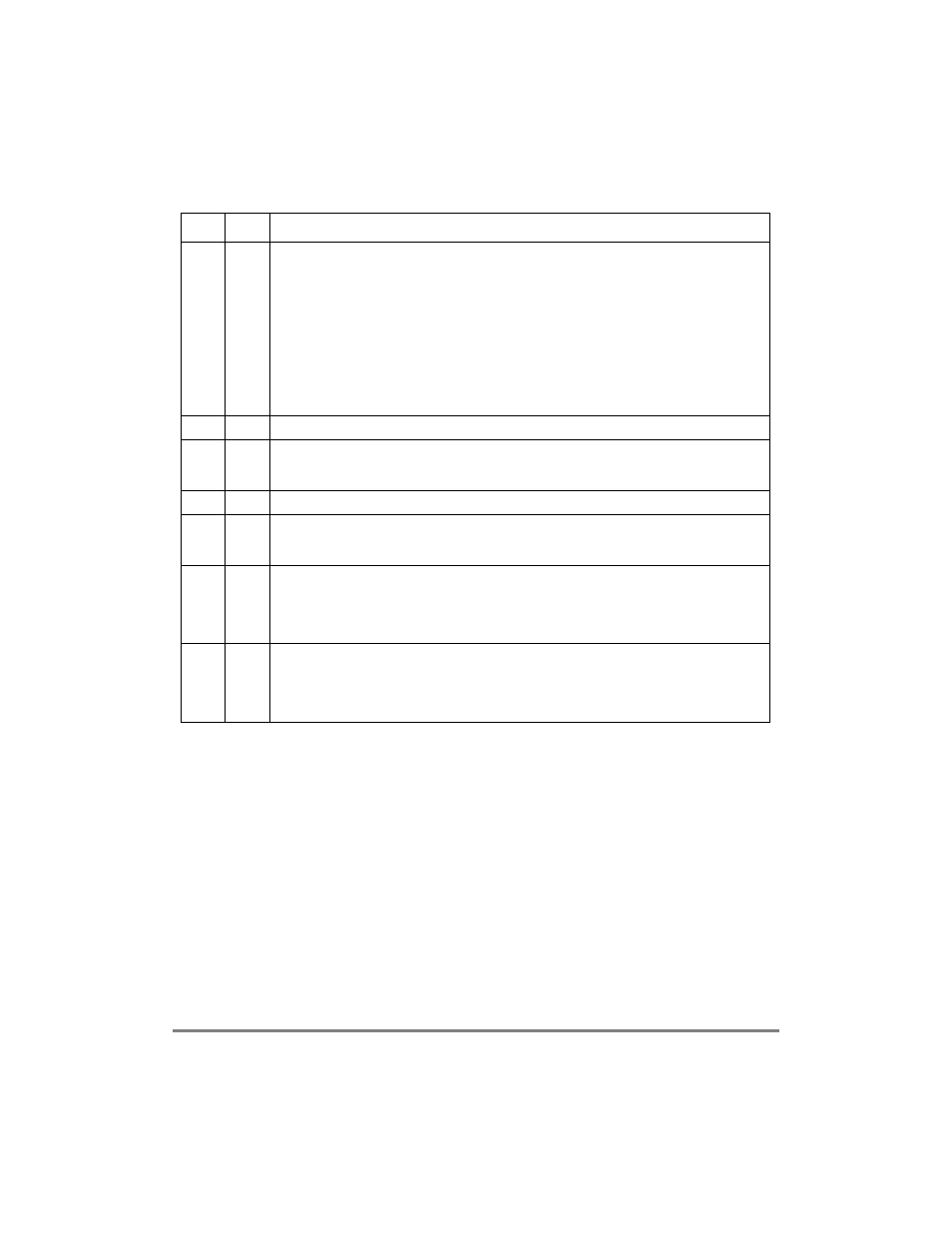

Table 27-5. CHAMR Field Descriptions (Continued)

Bits

Name Description