Motorola MPC8260 User Manual

Page 555

18-31

MPC8260 PowerQUICC II UserÕs Manual

MOTOROLA

Part IV. Communications Processor Module

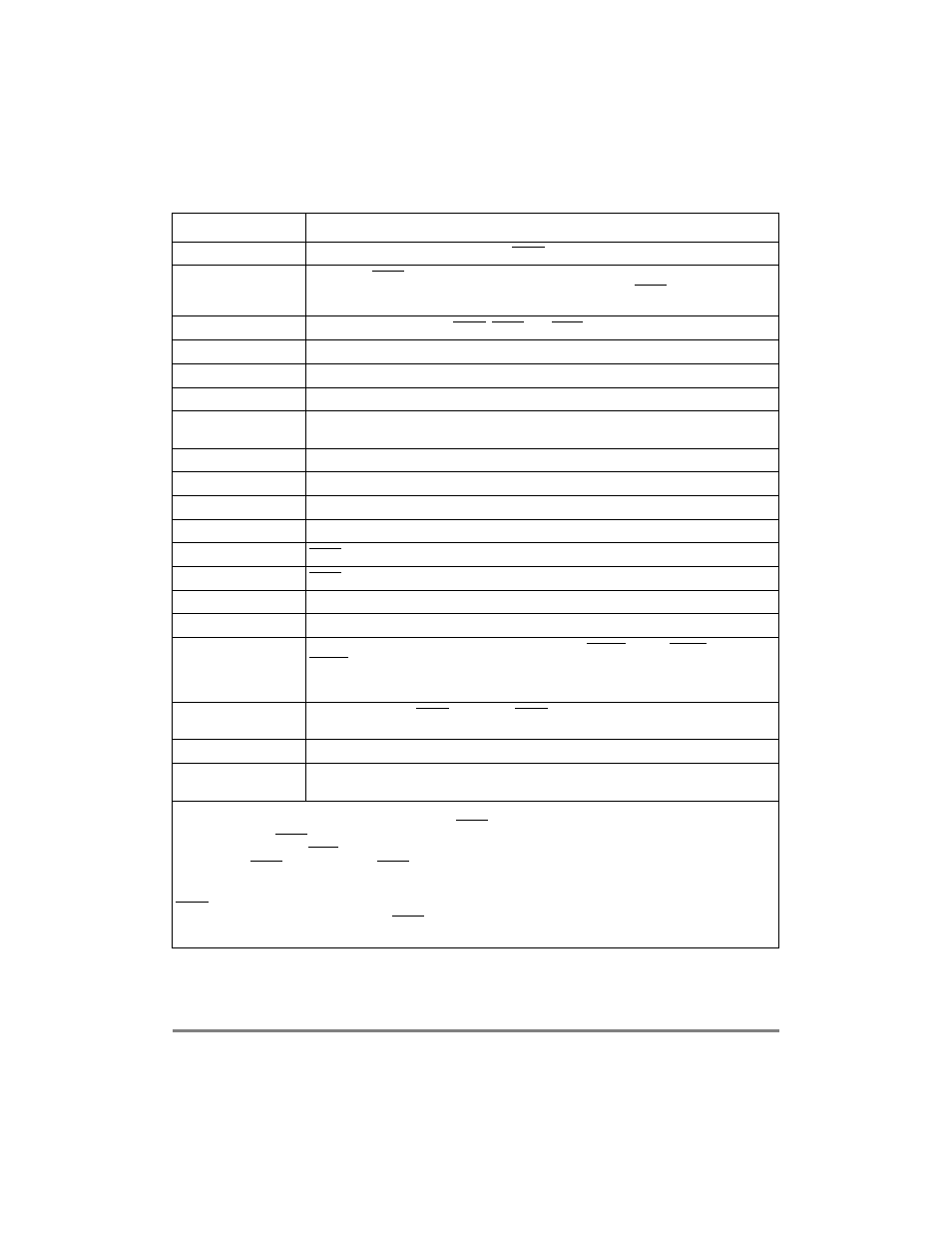

DCM[ERM] = 1

Transfers from peripheral are initiated by DREQ.

DCM[DT] = 1

Assertion of DONE by the peripheral terminates the transfer, interrupt EDN is set to the core,

Current BD is closed and the next BD if valid is opened. Additional DREQ assertions cause the

new BD to be transferred.

DCM[S/D] = 01

Memory-to-peripheral mode. DONE, DREQ, and DACK are connected to the peripheral.

DCM[SINC] = 1.

The memory address is incremented after every transfer.

DCM[DINC] = 1

The memory address is incremented after every transfer.

DPR_BUF

The IDMA transfer buffer is not used.

IBASE = IBDPTR =

0x0030

The current BD pointer is set to the BD table base address (aligned 16 -bits[3Ð0]=0000).

STS = 0x0004

Transfers from memory to peripheral are always 4 bytes long (60x singles).

DTS = 0x0004

Transfers from memory to peripheral are always 4 bytes long (60x singles).

Every BD[SDTB] = 1

Memory and peripheral are on the 60x bus.

Every BD[DDTB] = 1

Memory and peripheral are on the 60x bus.

Last BD[SDN] = 1

DONE is asserted on the last transfer.

Last BD[DDN] = 1

DONE is asserted on the last transfer.

IDMR3 = 0x0400_0000

The IDMA3 mask register is programmed to enable the IDSR[OB] interrupt only.

SIMR_L = 0x0000_0100

The interrupt controller is programmed to enable interrupts from IDMA3.

PDIRA = 0x2000_0000

PPARA = 0xE000_0000

PSORA = 0xE000_0000

PODRA = 0x4000_0000

Parallel I/O registers are programmed to enable:PA[0] = DREQ3; PA[2] = DACK3; PA[1] =

DONE3.

The peripheral signals are to be connected to these lines accordingly.

RCCR = 0x0000_0080

IDMA3 conÞguration: DREQ is level high. DONE is high to low. request priority is higher than

the SCCs.

89FE = 0x0300

IDMA3_BASE points to 0x0300 where the parameter table base address is located for IDMA3.

CPCR = 0x26C1_0009

START

_

IDMA

command. IDMA3 page-01001 SBC-10110 op-1001 FLG=1.This write starts the

channel operation.

DMA operation description:

START

_

IDMA

: Initialize all parameter RAM values, wait for DREQ to open the Þrst BD.

Steady state: Every DREQ triggers a 4-byte transfer in single address transaction. DMA performs a memory read

transaction combined with DACK assertion. Memory address is incremented constantly. Last transaction of the last BD is

combined with DONE assertion.Another DREQ assertion after last BD complete will issue IDSR[OB] interrupt to the core.

STOP

_

IDMA

: BD is closed. SC bit is set in IDSR (SC interrupt to the core is not enabled).Channel is stopped until

START

_

IDMA

command is issued.

DONE assertion by the peripheral: current BD is closed. IDSR[EDN] is set (but the interrupt to the core is not

enabled).The next BD is open with the next DREQ assertion (or IDSR[OB] interrupt is set to the core if there is no other

valid BDs).

Table 18-16. Example: Memory-to-Peripheral Fly-By Mode (on 60x)ÐIDMA3 (Continued)

Important Init Values

Description